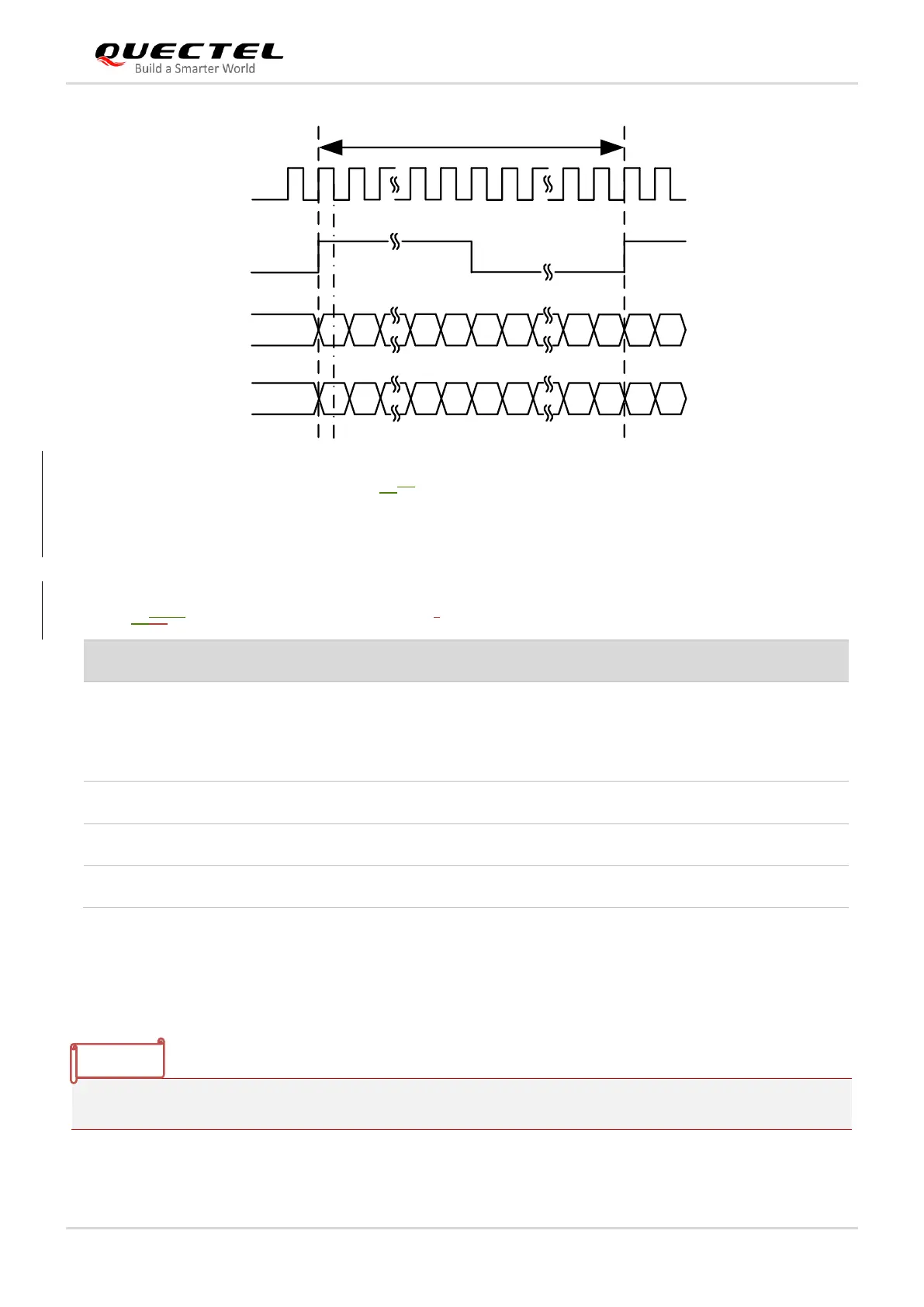

Figure 2122: Auxiliary Mode Timing

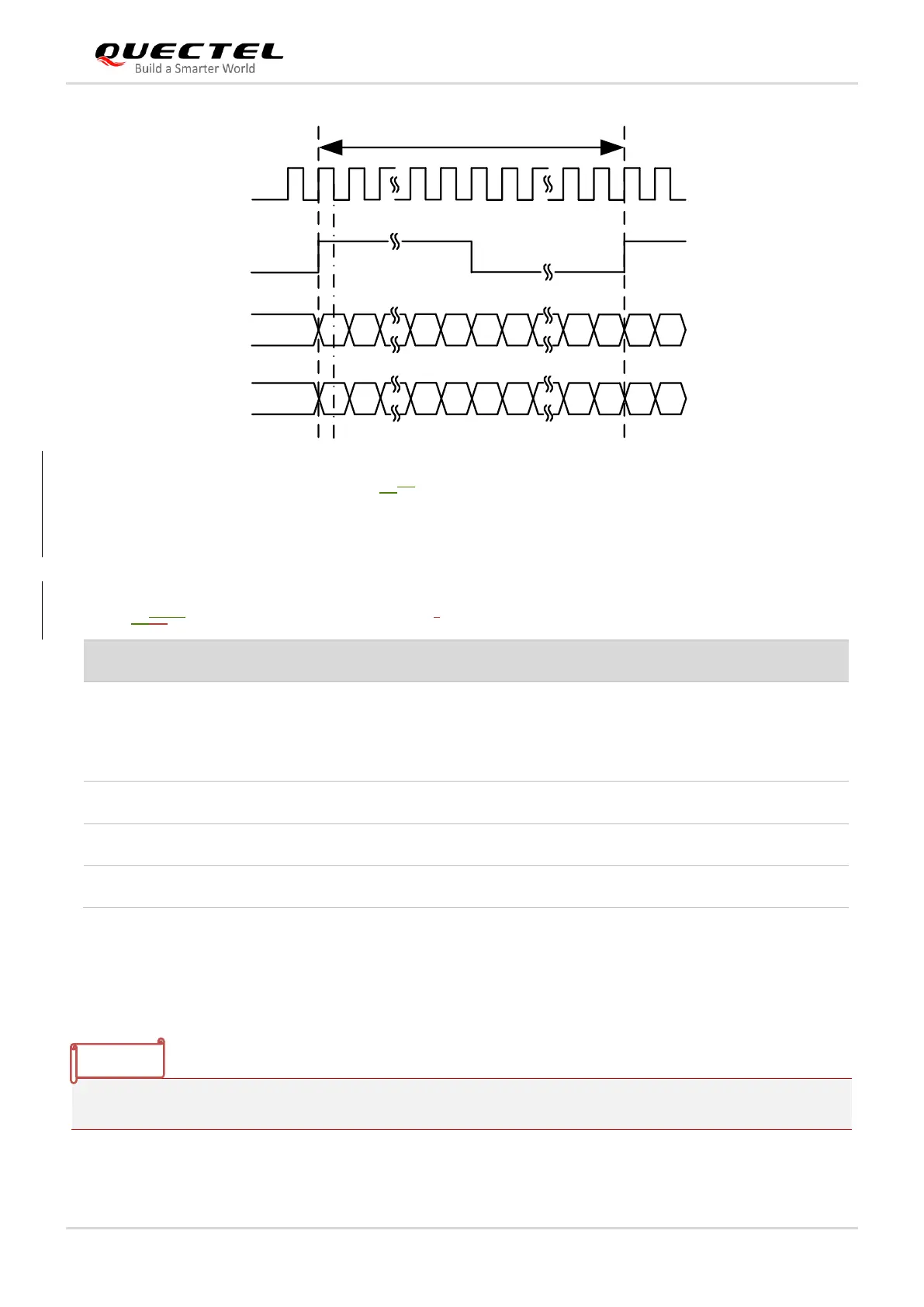

The following table shows the pin definition of PCM interface which can be applied to audio codec design.

Table 121211: Pin Definition of PCM Interface*

The clock and mode can be configured by AT command, and the default configuration is master mode

using short frame synchronization format with 2048 kHz PCM_CLK and 8 kHz PCM_SYNC. See

document [2] for details about AT+QDAI command.

1.8 V power domain

In master mode, it is an output signal.

In slave mode, it is an input signal.

If unused, keep it open.

Loading...

Loading...