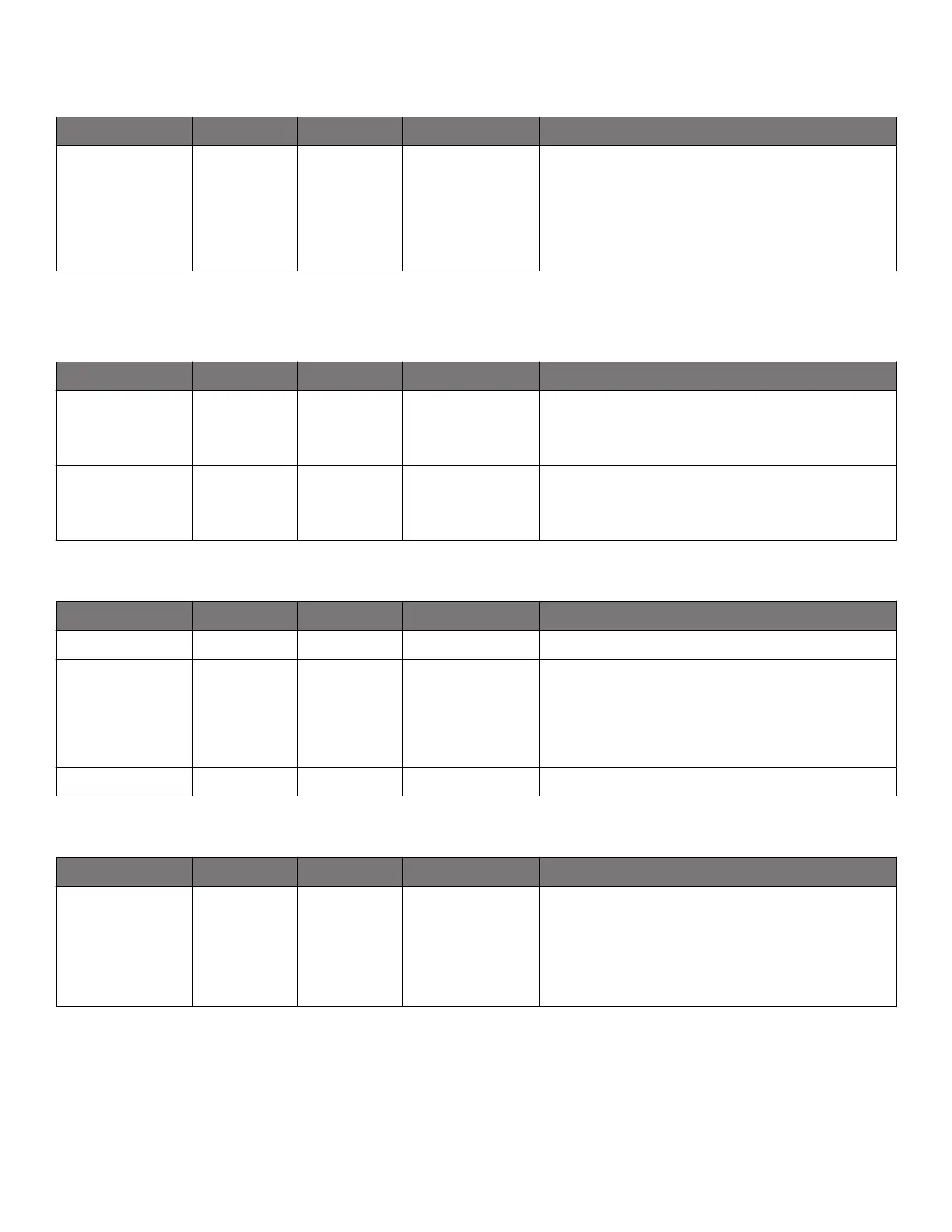

Table 14.107. 0x001C Soft Reset

Reg Address Bit Field Type Setting Name Description

0x001C 0 S SOFT_RST 1 Performs a soft rest. Resets the device while not re-

downloading the register configuration from NVM. If out-

put-output skew is needed and VDDOx does not come

up before VDD/VDDA then a soft reset will align the

output clocks.

0 No effect

This bits are of type “S”, which is self-clearing.

Table 14.108. 0x001D FINC, FDEC

Reg Address Bit Field Type Setting Name Description

0x001D 0 S FINC 1 A rising edge will cause a frequency increment. See

also N_FSTEP_MSK and Nx_FSTEPW

0 No effect

0x001D 1 S FDEC 1 A rising edge will cause a frequency decrement. See

also N_FSTEP_MSK and Nx_FSTEPW

0 No effect

Table 14.109. 0x001E Sync, Power Down and Hard Reset

Reg Address Bit Field Type Setting Name Description

0x001E 0 R/W PDN 1 to put the device into low power mode

0x001E 1 R/W HARD_RST 1 causes hard reset. The same as power up except

that the serial port access is not held at reset. NVM is

re-downloaded. This does not self-clear, so after setting

the bit it must be cleared.

0 No reset

0x001E 2 S SYNC 1 to reset all output R dividers to the same state

Table 14.110. 0x0021 Input Clock Selection

Reg Address Bit Field Type Setting Name Description

0x0021 0 R/W IN_SEL_REGCTRL Selects between register controlled reference clock se-

lection and pin controlled clock selection using IN_SEL1

and IN_SEL0 pins:

0 for pin controlled clock selection

1 for register clock selection

Si5341, Si5340 Rev D Family Reference Manual • Register Map

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

88 Rev. 1.3 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • July 26, 2021 88

Loading...

Loading...