Specifications

1-8

TDS5000B Series Specifications and Performance Verification

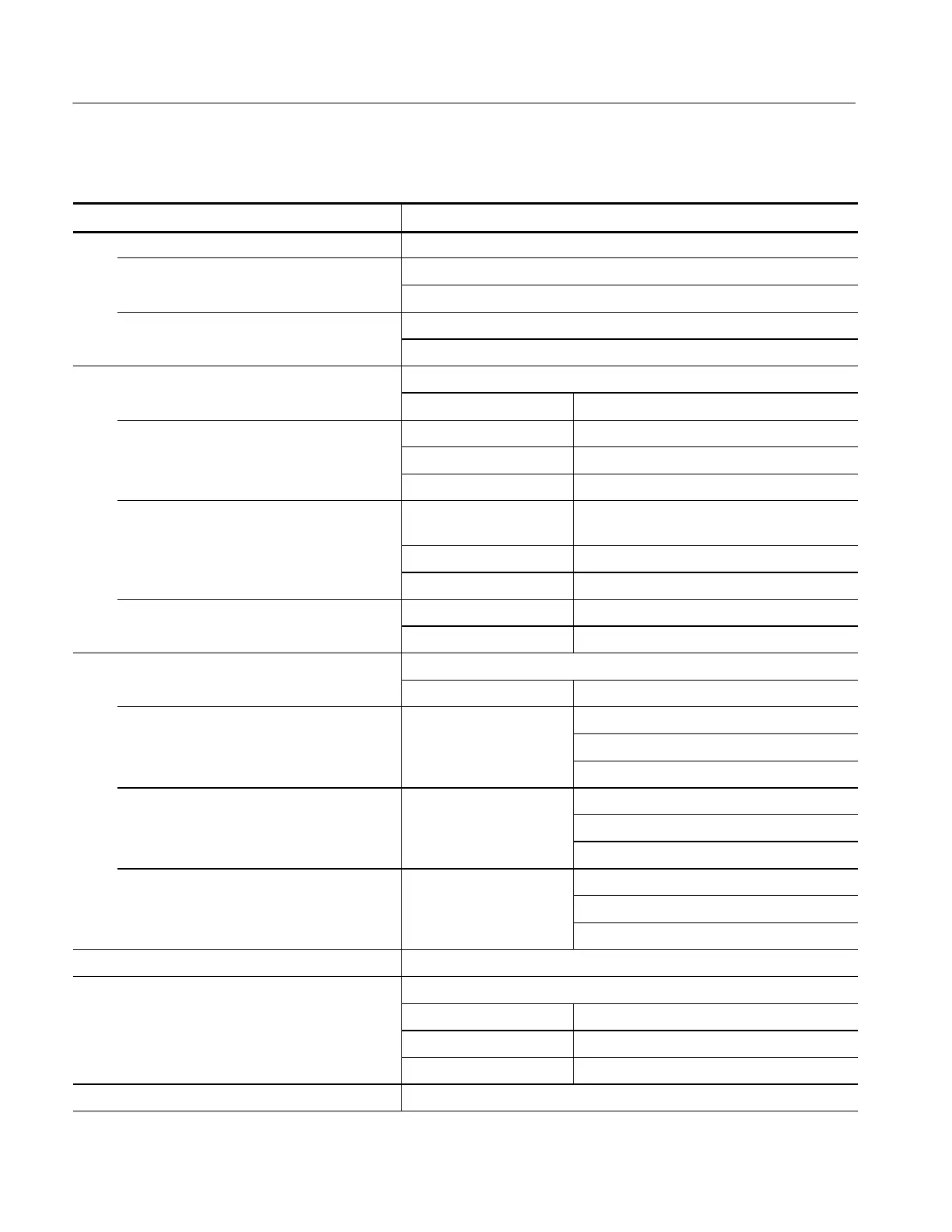

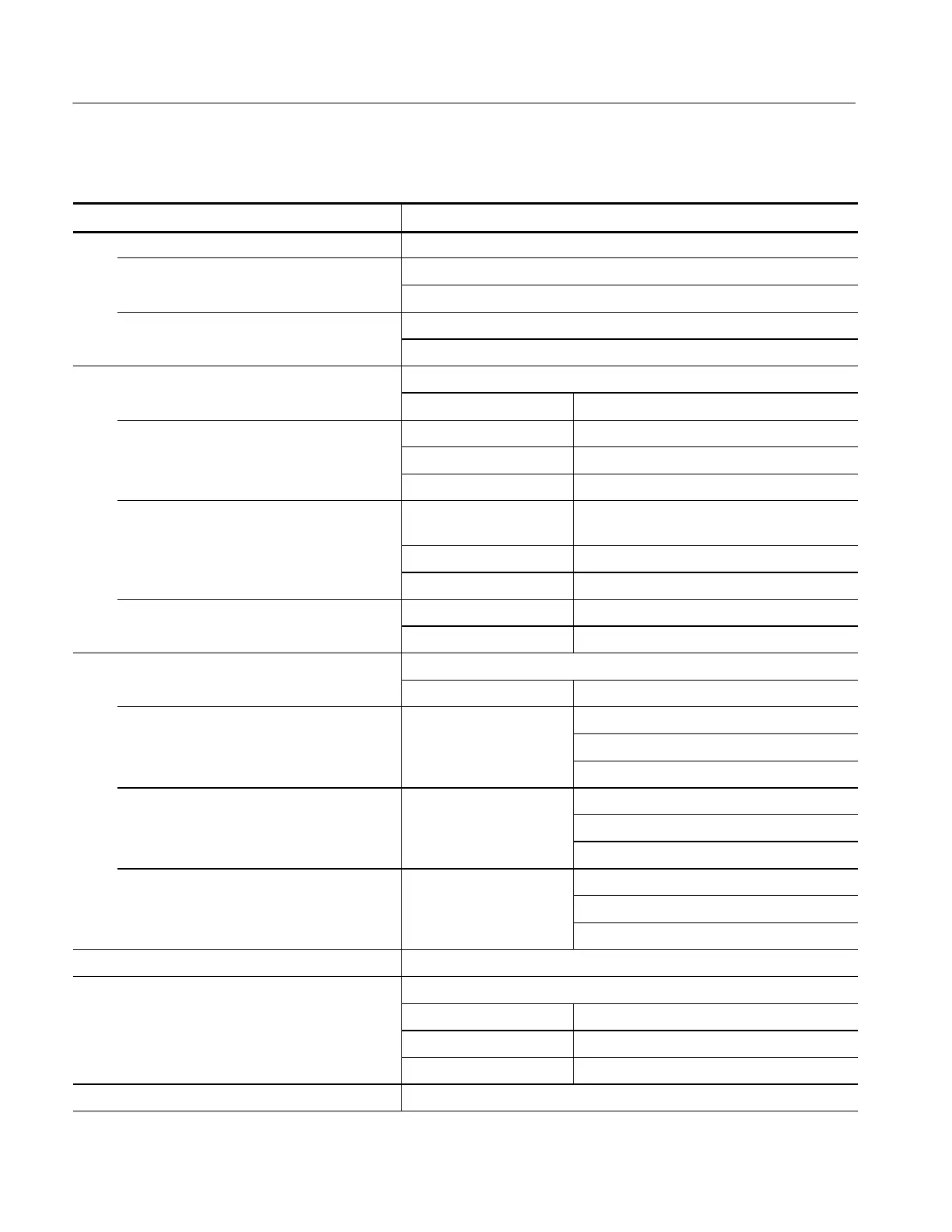

Table 1- 2: Channel input and vertical specifications (Cont.)

Characteri sti c Description

Analog Bandwidth Limit

Low frequency, AC coupled 50 Ω: <200 kHz

1MΩ: <10 Hz, reduced by a factor of ten when using a 10X probe

High frequency, typical 20 MHz: with 20 MHz bandwidt h limit turned on

150 MHz: with 150 MHz bandwidt h limit turned on

Calculated rise time, typical DC 50 Ω coupling, bandwidth limit set to Full

SCALE range Rise time

TDS5032B, TDS5034B 1mV/divto1.99mV/div 2.67 ns

2mV/divto4.98mV/div 1.6 ns

5mV/divto1V/div 1.15 ns

TDS5052B, TDS5054B,

TDS5054BE

1mV/divto1.99mV/div 2.29 ns

2mV/divto4.98mV/div 1.33 ns

5mV/divto1V/div 800 ps

TDS5104B 1mV/divto1.99mV/div 2.29 ns

2mV/divto1V/div 300 ps

Step response settling errors, t ypical Bandwidth limit set to Full

SCALE range Settling error at time after step

≤2 V step amplitude 1 mV/div to 99.5 mV/ div 20 ns: ≤0.5%

100 ns: ≤0.2%

20 ms: ≤0.1%

≤20 V step amplitude 100 mV/div to 1.0 V/div 20 ns: ≤1.0%

100 ns: ≤0.5%

20 ms: ≤0.2%

≤200 V step amplitude 1.01 V/div to 10 V/div 20 ns: ≤1.0%

100 ns: ≤0.5%

20 ms: ≤0.2%

Position range ±5 divisions

Peak Detect or Envelope Mode Pulse Response Capture of single event pulses

Number of channels Minimum pulse width

1or2 400 ps

3or4 800 ps

Offset range User-adjustabl e input offset voltages

Loading...

Loading...