Power Supplies

www.ti.com

8

SBAU090E–November 2003–Revised November 2018

Submit Documentation Feedback

Copyright © 2003–2018, Texas Instruments Incorporated

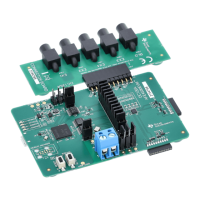

ADS1256EVM and ADS1256EVM-PDK

Figure 2. GPIO Pins

Each pin is connected to the GPIO header through a 100Ω resistor. 100kΩ pull-downs on each pin protect

the GPIOs when they are configured as inputs, which is the default setting. The GPIO header, J5, carries

the GPIO pins for the ADS1256.

The GPIO header pinout is described in Table 3.

Table 3. J5: GPIO Header Pins

Pin Number Pin Name Function

1 D0 GPIO or buffered system clock

output

2 D1 GPIO

3 D2 GPIO

4 D3 GPIO

4 Power Supplies

J5 is the power-supply input connector. It is used as the primary supply source for the entire EVM. Table 4

lists the configuration details for J2.

Table 4. J5 Configuration: Power-Supply Input

Pin No. Pin Name Function Required

J5.1 +VA Positive analog supply, +5V to

+18V

No

J5.2 –VA Negative analog supply, -5V to

-18V

No

J5.3 +5VA Positive analog supply, +5V Always

J5.4 –5VA Negative analog supply, -5V No

J5.5 DGND Digital ground Optional connection to

AGND through J10

J5.6 AGND Analog ground Ground

J5.7 +1.8VD Positive digital supply, +1.8V Digital supply; select

using J9

J5.8 VD1 Positive digital supply No

J5.9 +3.3VD Positive digital supply, +3.3V Digital supply; select

using J10

J5.10 +5VD Positive digital supply, +5V No

Loading...

Loading...