www.ti.com

Enabling Use of the SAFE Pin

35

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Permanent Fail

1 = Enabled

0 = Disabled (default)

VIMR (Bit 5): Voltage Imbalance at Rest

1 = Enabled

0 = Disabled (default)

SOT (Bit 4): Safety Overtemperature Cell

1 = Enabled

0 = Disabled (default)

SOCD (Bit 3): Safety Overcurrent in Discharge

1 = Enabled

0 = Disabled (default)

SOCC (Bit 2): Safety Overcurrent in Charge

1 = Enabled

0 = Disabled (default)

SOV (Bit 1): Safety Overvoltage

1 = Enabled

0 = Disabled (default)

SUV (Bit 0): Safety Undervoltage

1 = Enabled

0 = Disabled (default)

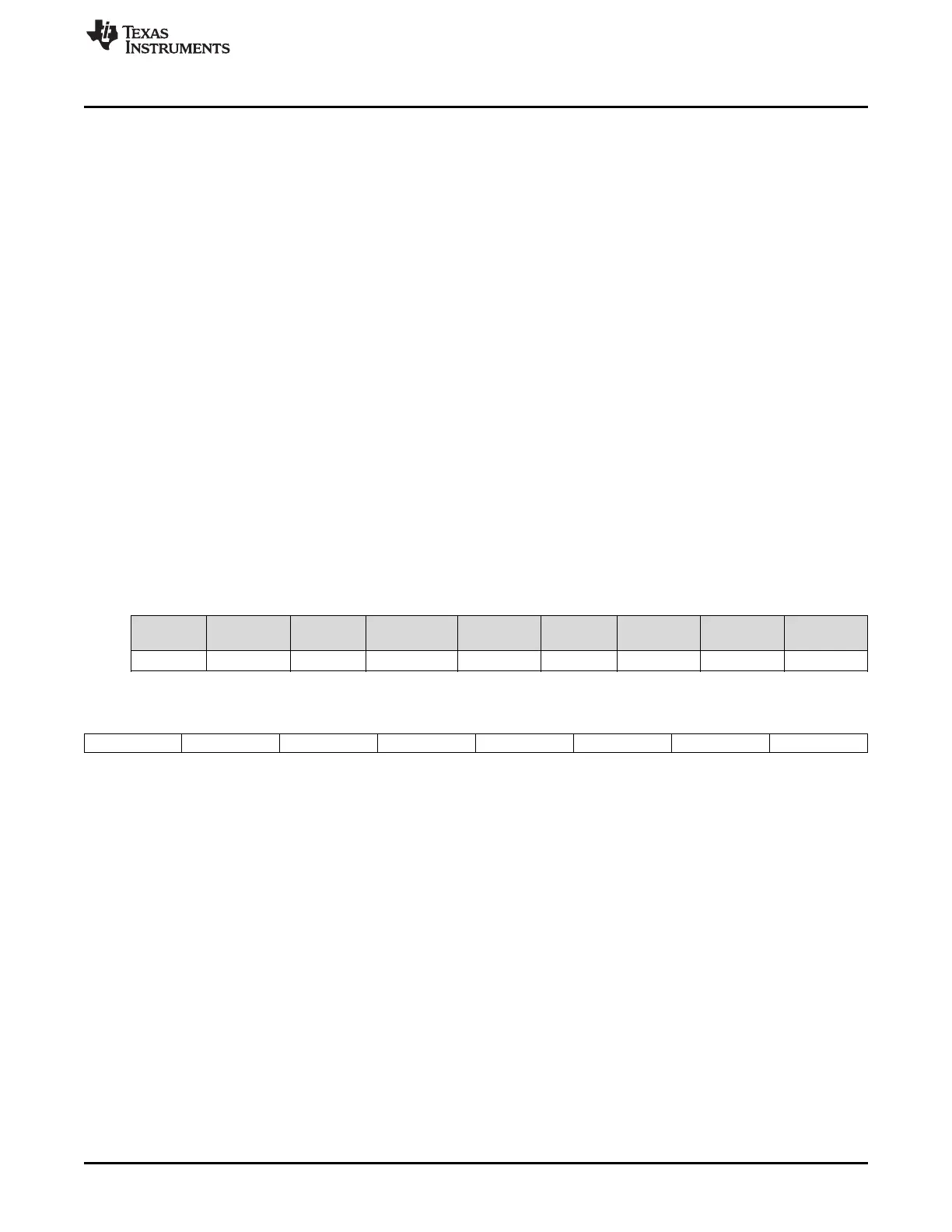

Class Subclass Name Format

Size in

Bytes

Min Max Default Unit

Settings Fuse PF SAFE B Hex 1 0x00 0xFF 0x00 —

7 6 5 4 3 2 1 0

SOTF TS3 TS2 TS1 AFE_XRDY AFE_OVRD AFEC AFER

SOTF (Bit 7): Safety Overtemperature FET

1 = Enabled

0 = Disabled (default)

TS3 (Bit 6): TS3

1 = Enabled

0 = Disabled (default)

TS2 (Bit 5): TS2

1 = Enabled

0 = Disabled (default)

TS1 (Bit 4): TS1

1 = Enabled

0 = Disabled (default)

AFE_XRDY (Bit 3): AFE XREADY

1 = Enabled

0 = Disabled (default)

Loading...

Loading...