15

TMS320F28069

,

TMS320F28068

,

TMS320F28067

,

TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com

SPRS698F –NOVEMBER 2010–REVISED MARCH 2016

Submit Documentation Feedback

Product Folder Links: TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

Terminal Configuration and FunctionsCopyright © 2010–2016, Texas Instruments Incorporated

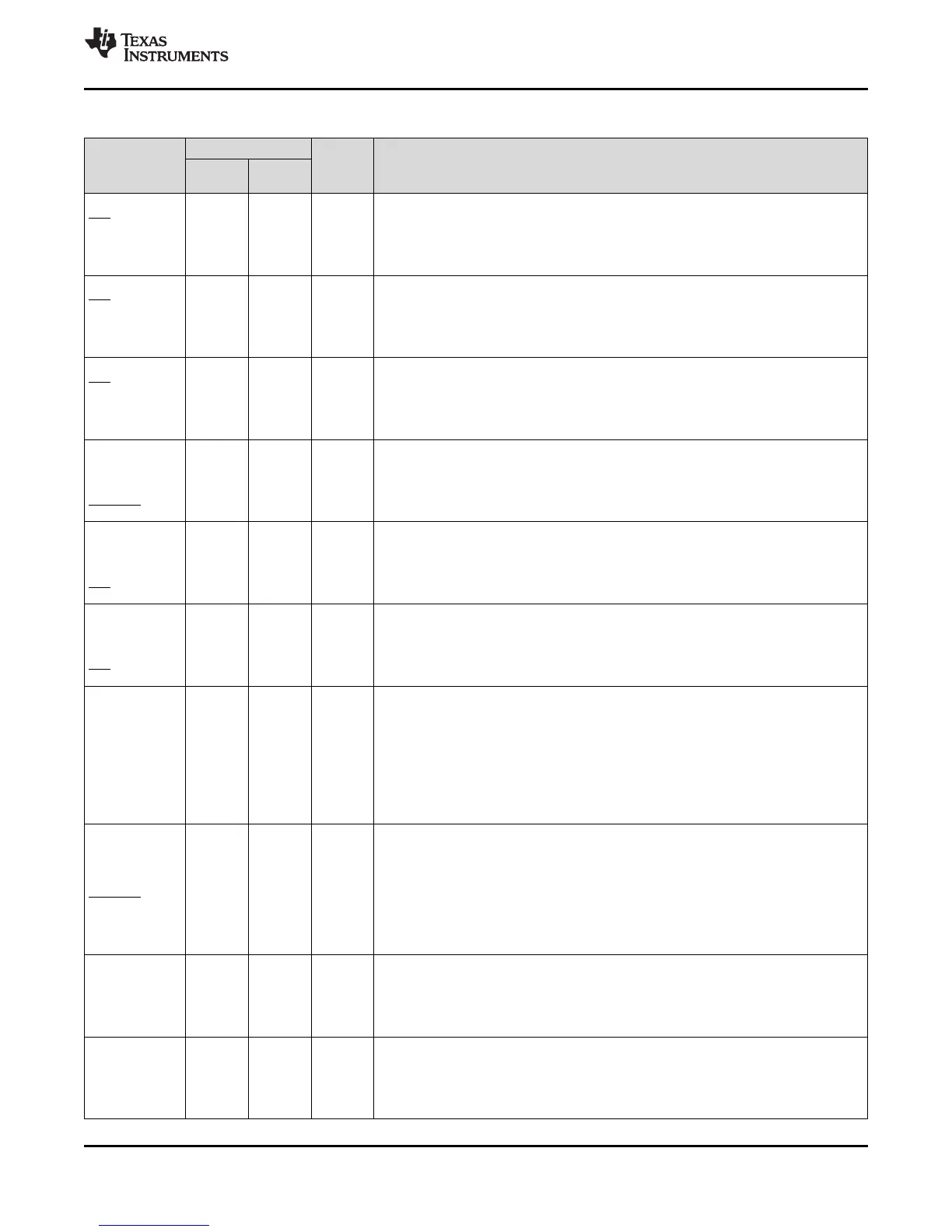

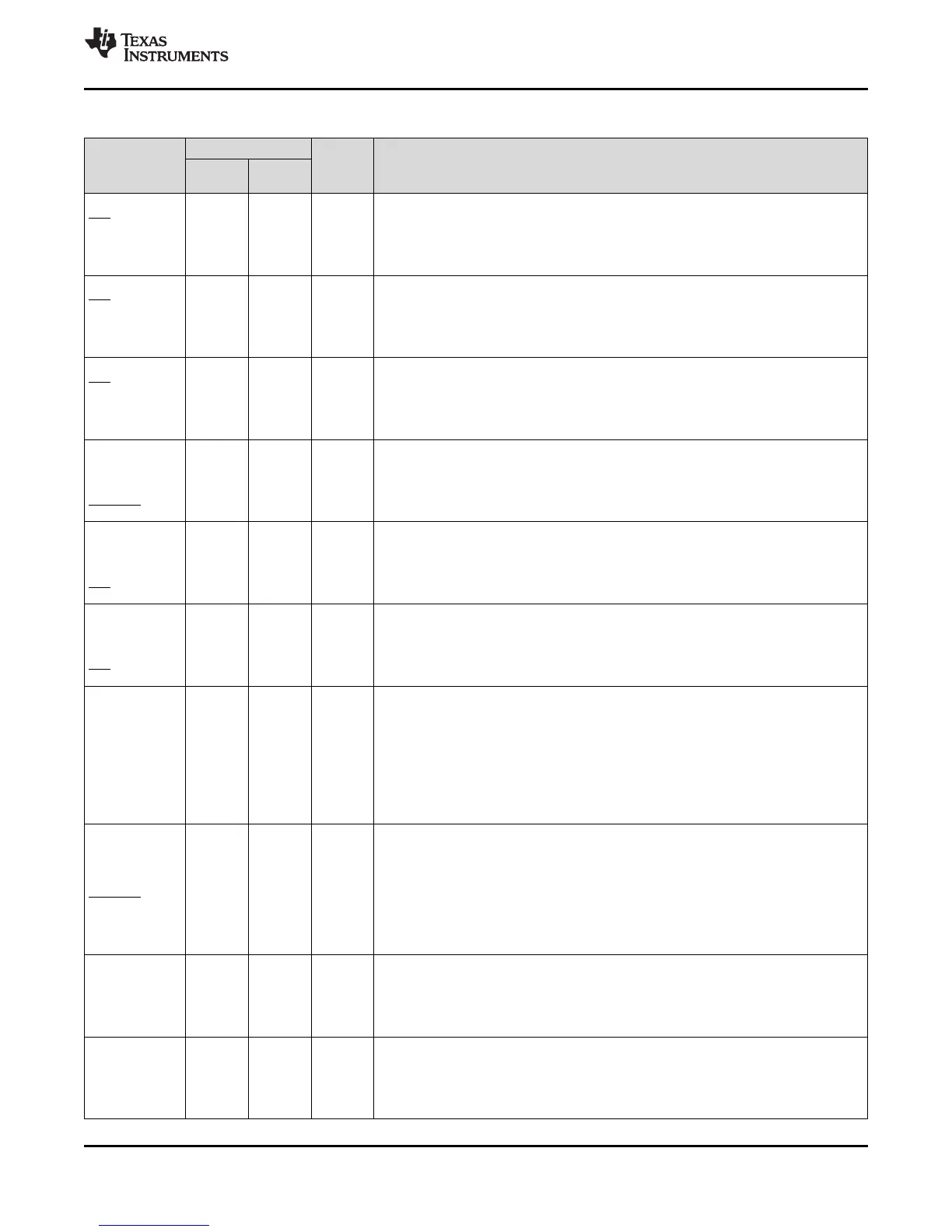

Table 4-1. Signal Descriptions

(1)

(continued)

PIN NAME

PIN NO.

I/O/Z DESCRIPTION

PZ

PZP

PN

PFP

GPIO12

44 35

I/O/Z General-purpose input/output 12

TZ1 I Trip Zone input 1

SCITXDA O SCI-A transmit data

SPISIMOB I/O SPI-B slave in, master out

GPIO13

95 75

I/O/Z General-purpose input/output 13

TZ2 I Trip Zone input 2

Reserved – Reserved

SPISOMIB I/O SPI-B slave out, master in

GPIO14

96 76

I/O/Z General-purpose input/output 14

TZ3 I Trip zone input 3

SCITXDB O SCI-B transmit data

SPICLKB I/O SPI-B clock input/output

GPIO15

88 70

I/O/Z General-purpose input/output 15

ECAP2 I/O Enhanced Capture input/output 2

SCIRXDB I SCI-B receive data

SPISTEB I/O SPI-B slave transmit enable input/output

GPIO16

55 44

I/O/Z General-purpose input/output 16

SPISIMOA I/O SPI-A slave in, master out

Reserved – Reserved

TZ2 I Trip Zone input 2

GPIO17

52 42

I/O/Z General-purpose input/output 17

SPISOMIA I/O SPI-A slave out, master in

Reserved – Reserved

TZ3 I Trip zone input 3

GPIO18

51 41

I/O/Z General-purpose input/output 18

SPICLKA I/O SPI-A clock input/output

SCITXDB O SCI-B transmit data

XCLKOUT

O/Z

Output clock derived from SYSCLKOUT. XCLKOUT is either the same frequency, one-

half the frequency, or one-fourth the frequency of SYSCLKOUT. This is controlled by

bits 1:0 (XCLKOUTDIV) in the XCLK register. At reset, XCLKOUT = SYSCLKOUT/4.

The XCLKOUT signal can be turned off by setting XCLKOUTDIV to 3. The mux control

for GPIO18 must also be set to XCLKOUT for this signal to propogate to the pin.

GPIO19

64 52

I/O/Z General-purpose input/output 19

XCLKIN

I

External Oscillator Input. The path from this pin to the clock block is not gated by the

mux function of this pin. Care must be taken not to enable this path for clocking if it is

being used for the other peripheral functions.

SPISTEA I/O SPI-A slave transmit enable input/output

SCIRXDB I SCI-B receive data

ECAP1 I/O Enhanced Capture input/output 1

GPIO20

6 5

I/O/Z General-purpose input/output 20

EQEP1A I Enhanced QEP1 input A

MDXA O McBSP transmit serial data

COMP1OUT O Direct output of Comparator 1

GPIO21

7 6

I/O/Z General-purpose input/output 21

EQEP1B I Enhanced QEP1 input B

MDRA I McBSP receive serial data

COMP2OUT O Direct output of Comparator 2

Loading...

Loading...