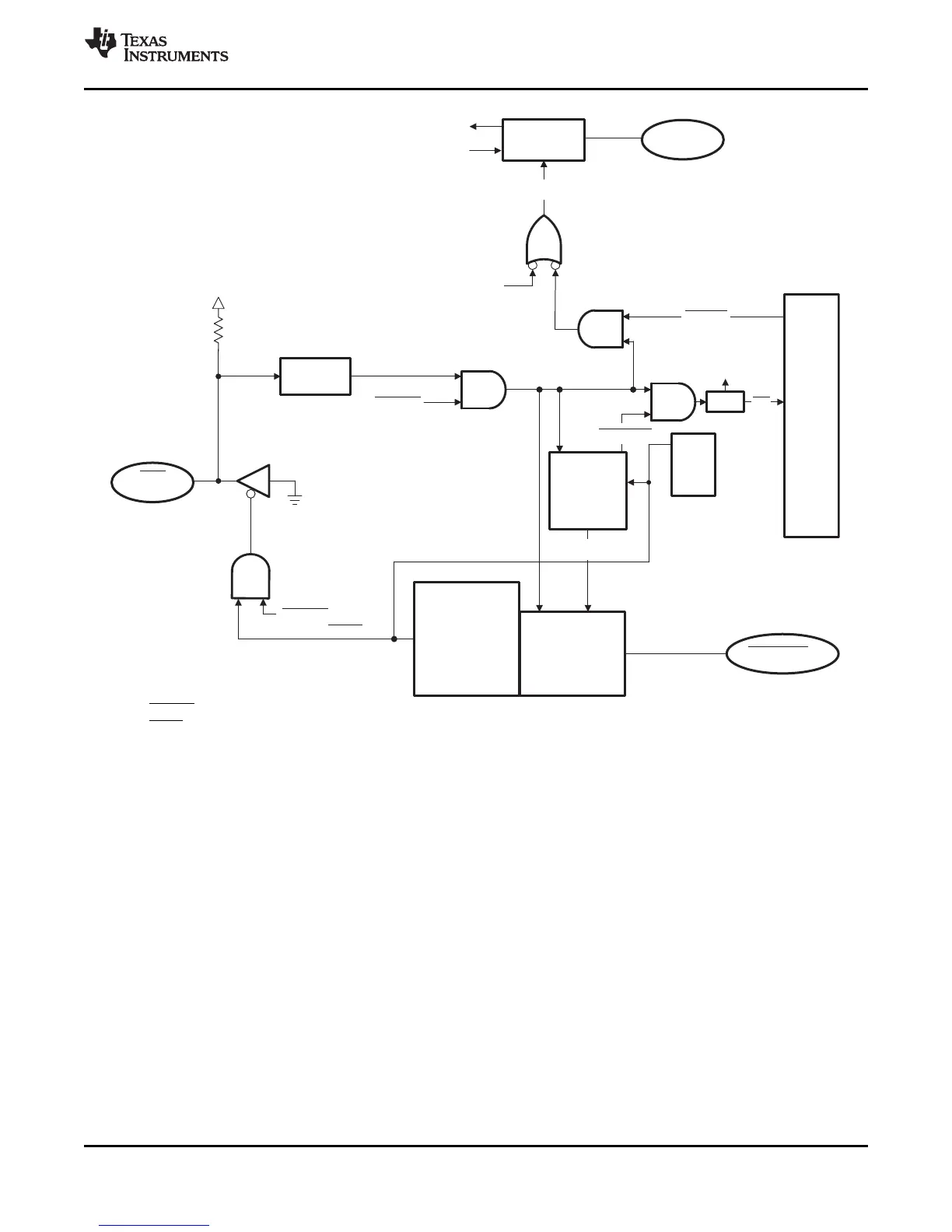

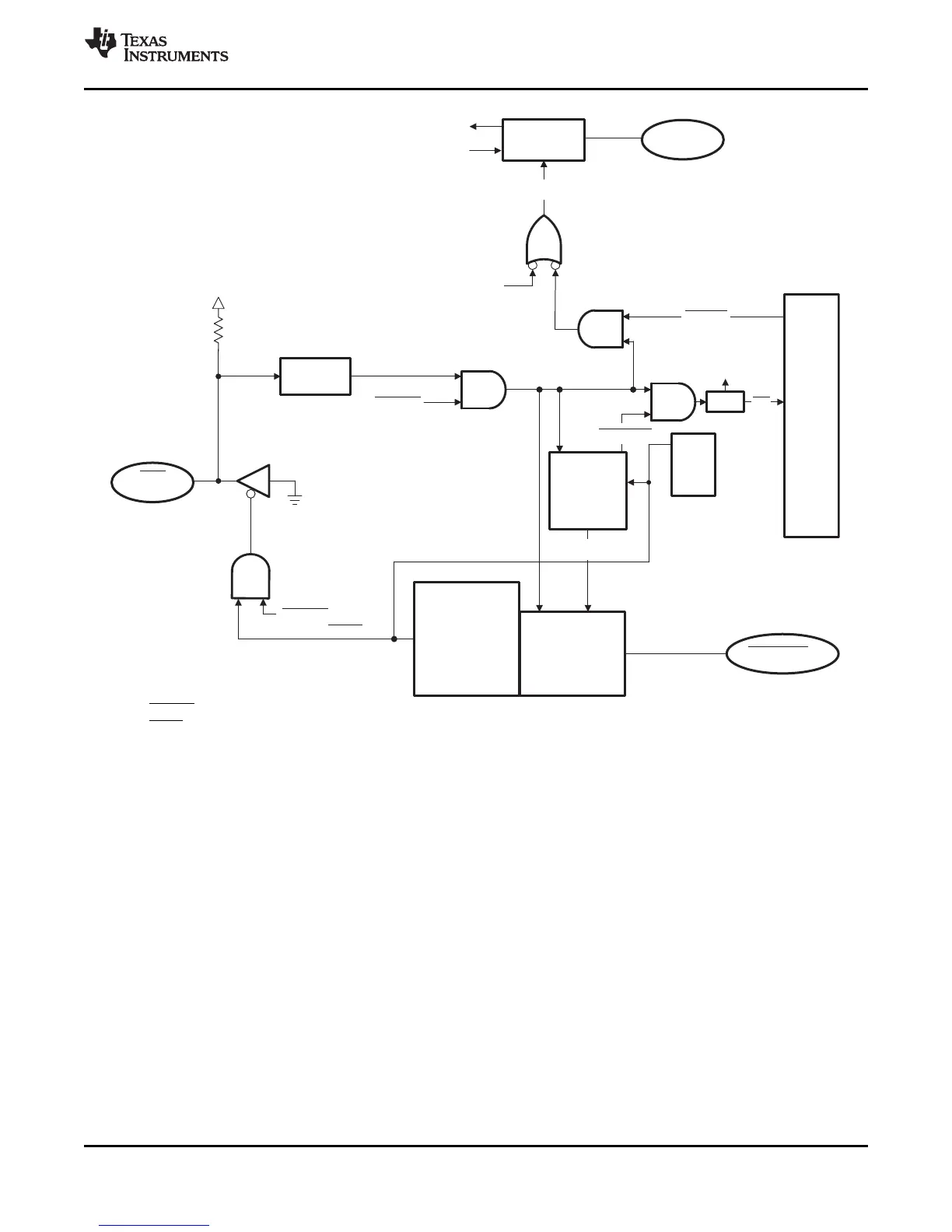

I/O Pin

In

Out

DIR (0 = Input, 1 = Output)

(Force Hi-Z When High)

SYSRS

C28

Core

Sync

RS

PLL

+

Clocking

Logic

MCLKRS

VREGHALT

Deglitch

Filter

On-Chip

Voltage

Regulator

(VREG)

VREGENZ

POR/BOR

Generating

Module

XRS

Pin

WDRST

SYSCLKOUT

WDRST

(A)

JTAG

TCK

Detect

Logic

PBRS

(B)

Internal

Weak PU

63

TMS320F28069

,

TMS320F28068

,

TMS320F28067

,

TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com

SPRS698F –NOVEMBER 2010–REVISED MARCH 2016

Submit Documentation Feedback

Product Folder Links: TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

Detailed DescriptionCopyright © 2010–2016, Texas Instruments Incorporated

A. WDRST is the reset signal from the CPU-watchdog.

B. PBRS is the reset signal from the POR/BOR module.

Figure 6-9. VREG + POR + BOR + Reset Signal Connectivity

Loading...

Loading...