Manual VIPA System 300S SPEED7 Chapter 5 Deployment I/O periphery

HB140E - CPU SC - RE_313-6CF03 - Rev. 07/45 5-13

... continued

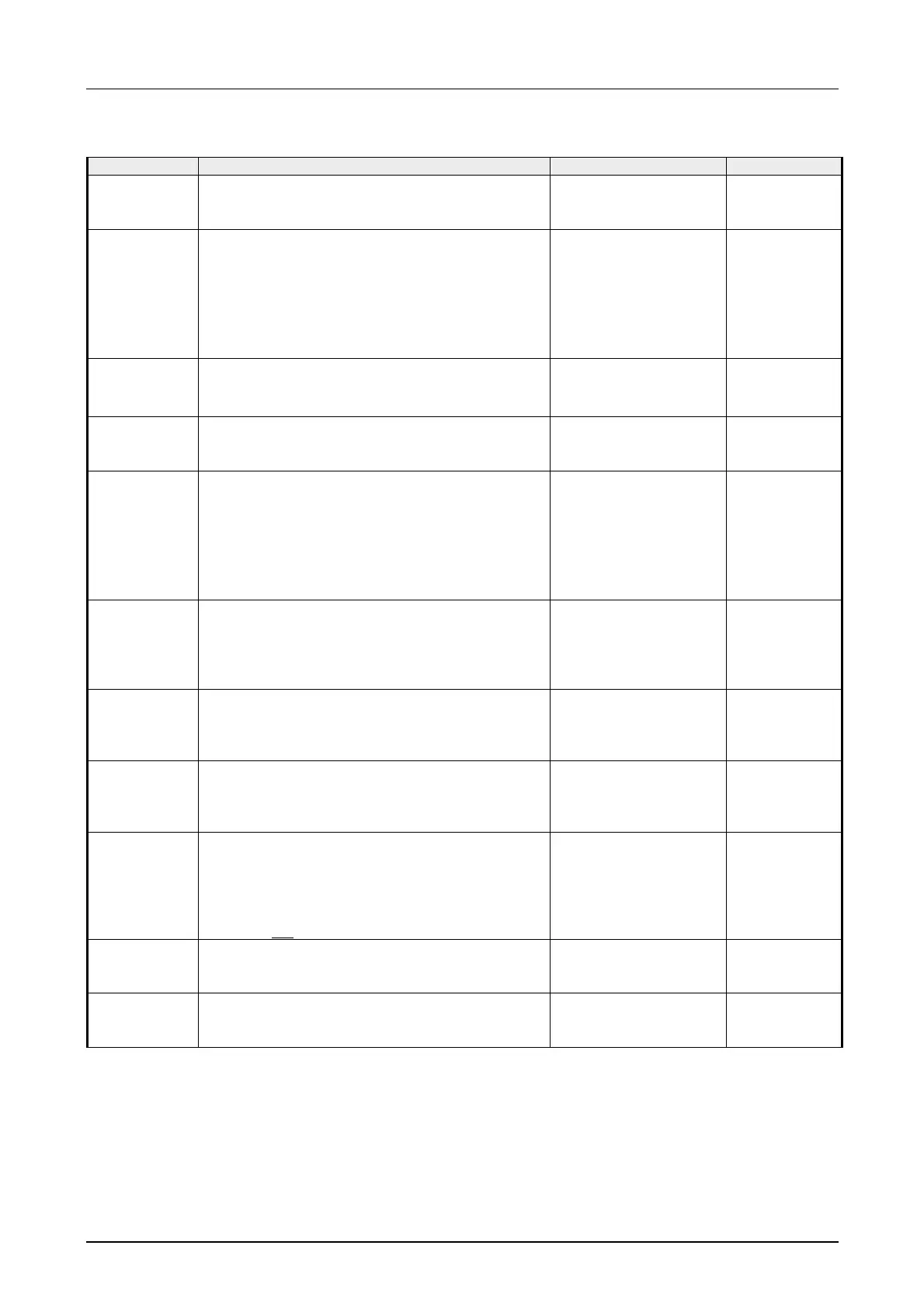

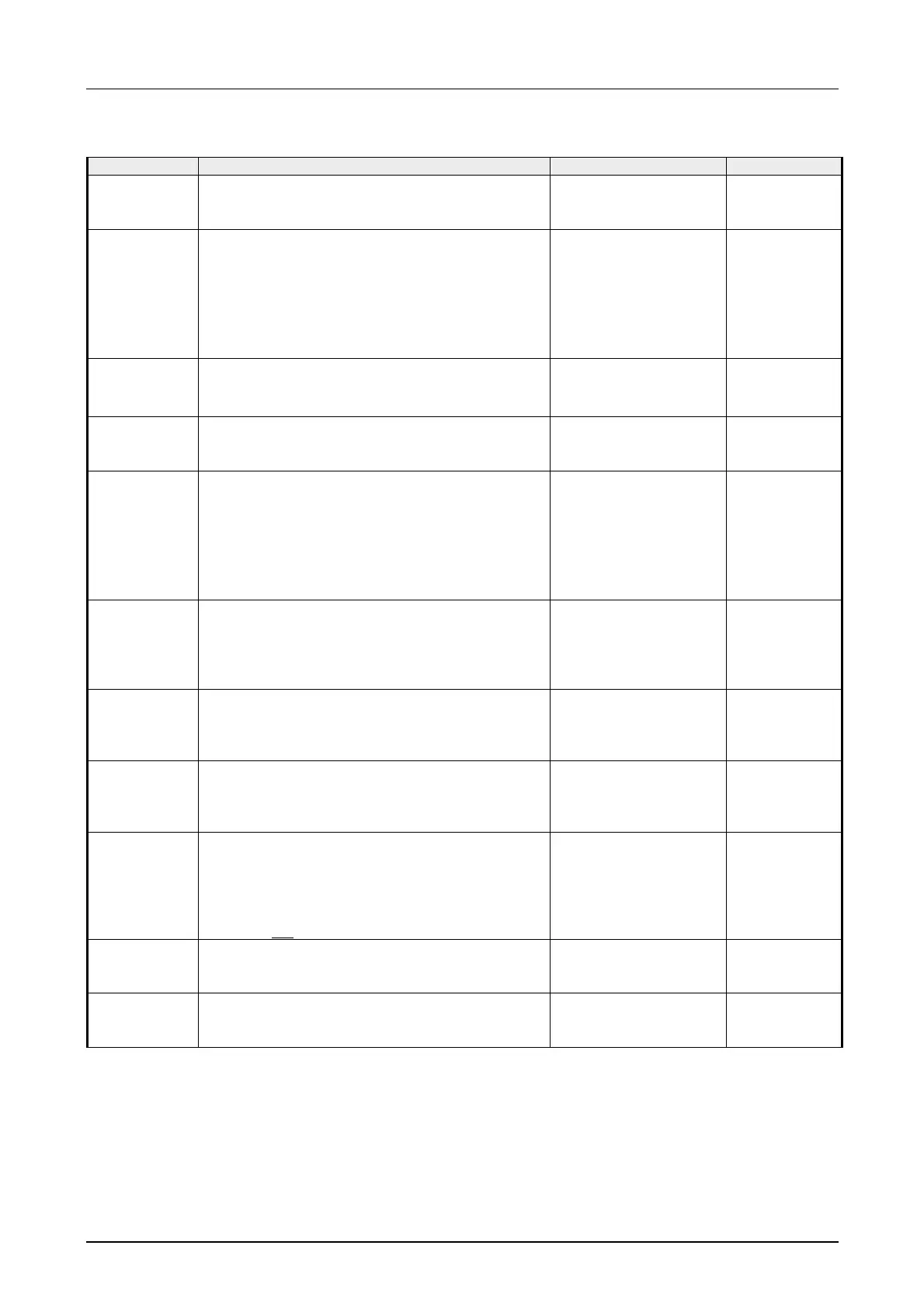

Parameters Description Range of value Default

max.

frequency:

Latch

You can set the maximum frequency of the latch

signal in fixed steps.

30, 10, 5, 2, 1kHz 10kHz

Signal

evaluation

The count and direction signals are connected to

the input.

A rotary transducer is connected to the input

(single, dual or quadruple evaluation).

• Pulse/Direction

• Rotary encoder

single

• Rotary encoder,

double

• Rotary encoder

quadruple

Pulse/Direction

Hardware

gate

In the activated state the Gate control is made via

SW-gate and HW-gate, otherwise via SW-gate

only.

• activated

• deactivated

deactivated

Count

direction

inverted

In the activated state the "direction" input signal is

inverted.

• activated

• deactivated

deactivated

Characteristics

of the output

The output and the "Comparator" (STS_CMP)

status bit are set, dependent on this parameter.

• No comparison

• Count ≥

comparison value

• Count ≤

comparison value

• Pulse at

comparison value

No comparison

Pulse duration With the setting "Characteristics of the output:

Pulse at comparison value" the pulse duration of

the output signal may be specified.

Only even values are possible. The value is

internal multiplied with 1.024ms.

0 to 510 0

Hardware

interrupt:

Hardware

gate opening

In the activated state a hardware interrupt is

generated when the hardware gate opens while

the software gate is open.

• activated

• deactivated

Hardware

interrupt:

Hardware

gate closing

In the activated state a hardware interrupt is

generated when the hardware gate closes while

the software gate is open.

• activated

• deactivated

deactivated

Hardware

interrupt:

On reaching

comparator

In the activated state a hardware interrupt is

triggered on reaching the comparator (reaction)

value.

The process interrupt may only be released if in

addition the value of "Characteristics of the

output" is not

"no comparison".

• activated

• deactivated

deactivated

Hardware

interrupt:

Overflow

In the activated state a hardware interrupt is

generated in the event of an overflow (exceeding

the upper count limit).

• activated

• deactivated

deactivated

Hardware

interrupt:

Underflow

In the activated state a hardware interrupt is

generated in the event of an underflow

(undershooting the lower count limit).

• activated

• deactivated

deactivated

Loading...

Loading...