KCU105 Board User Guide www.xilinx.com 20

UG917 (v1.4) September 25, 2015

Chapter 1: KCU105 Evaluation Board Features

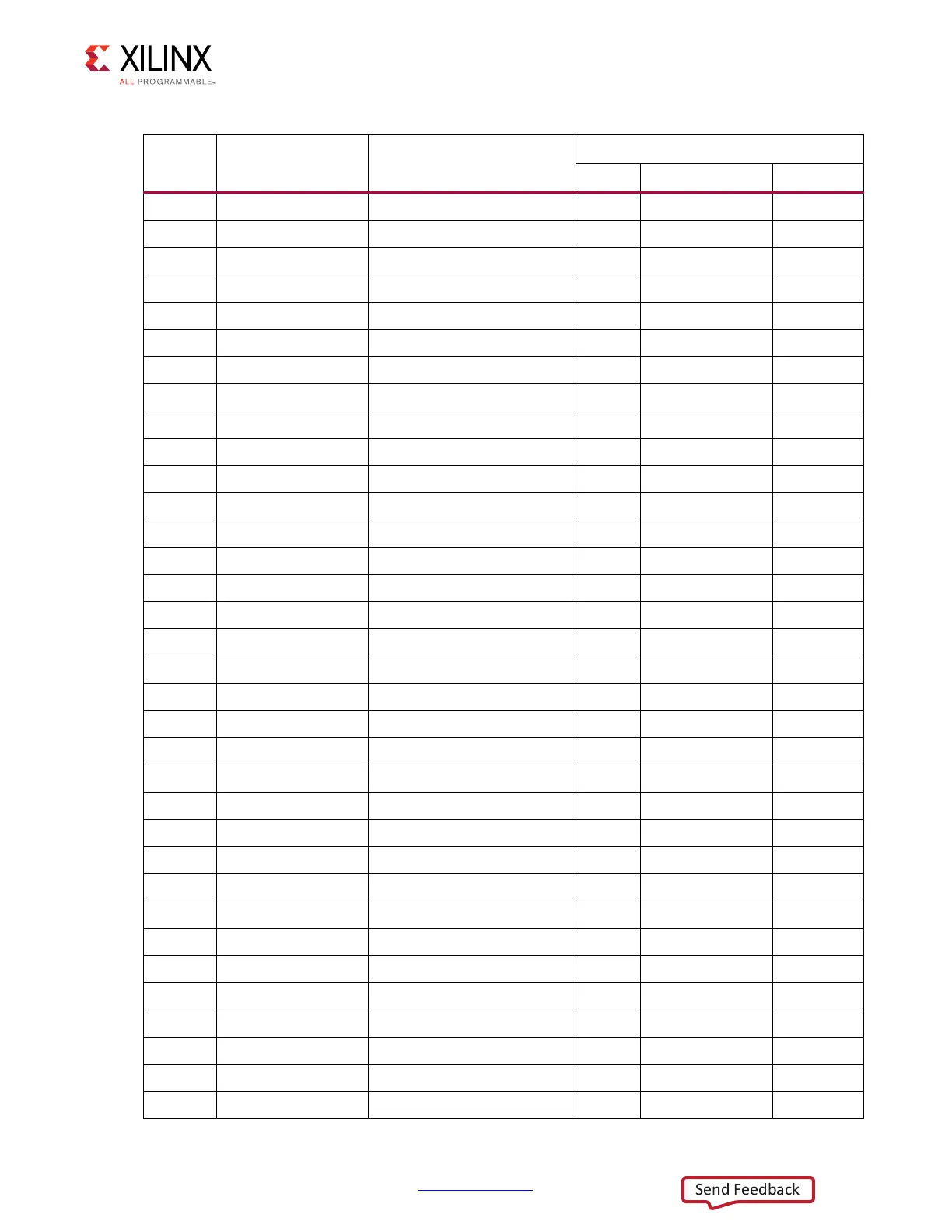

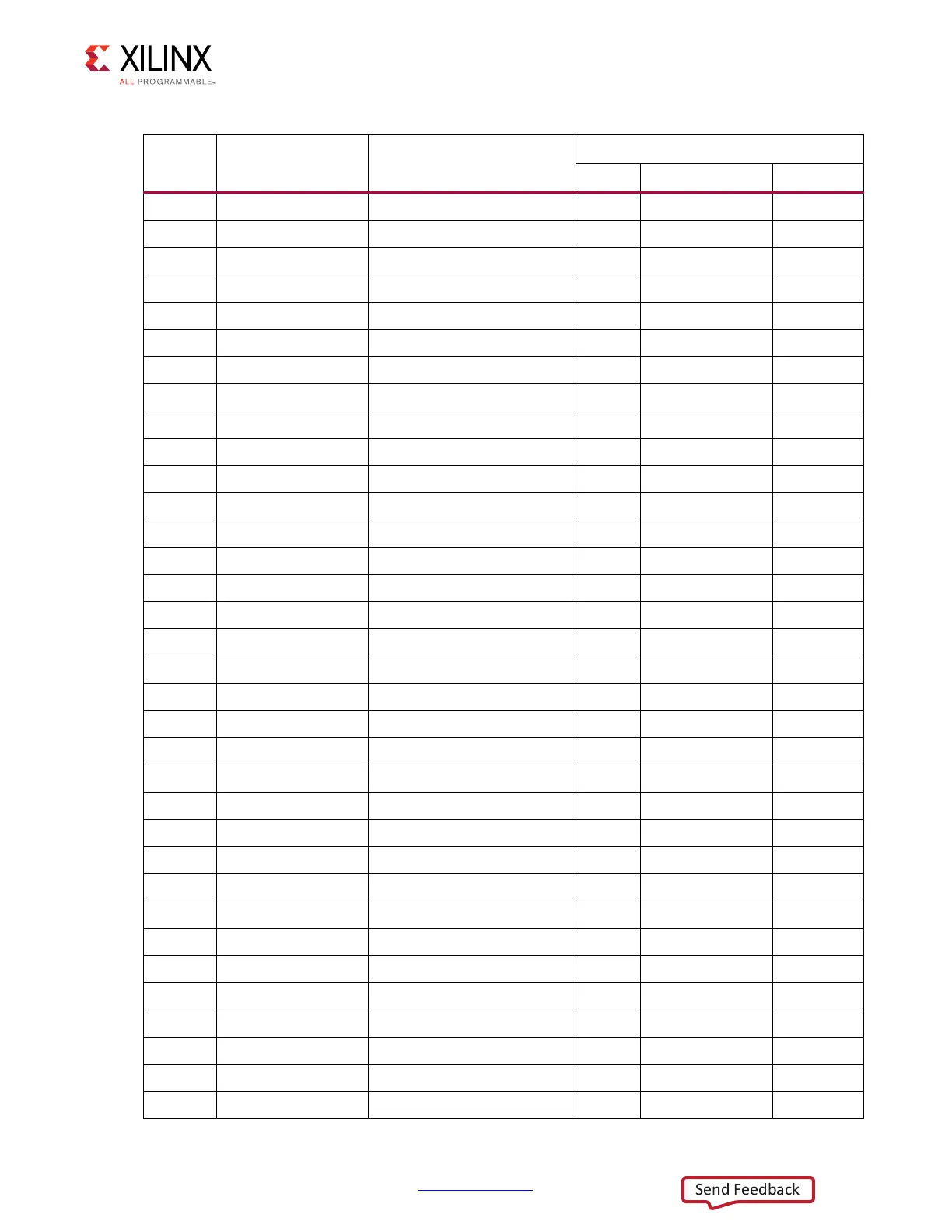

AN31 DDR4_DQ61 POD12_DCI C8 DQU5 U63

AL34 DDR4_DQ62 POD12_DCI D3 DQU6 U63

AN32 DDR4_DQ63 POD12_DCI D7 DQU7 U63

AH33 DDR4_DQS6_T DIFF_POD12_DCI G3 DQSL_T U63

AJ33 DDR4_DQS6_C DIFF_POD12_DCI F3 DQSL_C U63

AN34 DDR4_DQS7_T DIFF_POD12_DCI B7 DQSU_T U63

AP34 DDR4_DQS7_C DIFF_POD12_DCI A7 DQSU_C U63

AJ29 DDR4_DM6 POD12_DCI E7 DML_B/DBIL_B U63

AL32 DDR4_DM7 POD12_DCI E2 DMU_B/DBIU_B U63

AE17 DDR4_A0 SSTL12_DCI P3 A0 U60-U62

AH17 DDR4_A1 SSTL12_DCI P7 A1 U60-U62

AE18 DDR4_A2 SSTL12_DCI R3 A2 U60-U62

AJ15 DDR4_A3 SSTL12_DCI N7 A3 U60-U62

AG16 DDR4_A4 SSTL12_DCI N3 A4 U60-U62

AL17 DDR4_A5 SSTL12_DCI P8 A5 U60-U62

AK18 DDR4_A6 SSTL12_DCI P2 A6 U60-U62

AG17 DDR4_A7 SSTL12_DCI R8 A7 U60-U62

AF18 DDR4_A8 SSTL12_DCI R2 A8 U60-U62

AH19 DDR4_A9 SSTL12_DCI R7 A9 U60-U62

AF15 DDR4_A10 SSTL12_DCI M3 A10/AP U60-U62

AD19 DDR4_A11 SSTL12_DCI T2 A11 U60-U62

AJ14 DDR4_A12 SSTL12_DCI M7 A12/BC_B U60-U62

AG19 DDR4_A13 SSTL12_DCI T8 A13 U60-U62

AD16 DDR4_A14_WE_B SSTL12_DCI L2 WE_B/A14 U60-U62

AG14 DDR4_A15_CAS_B SSTL12_DCI M8 CAS_B/A15 U60-U62

AF14 DDR4_A16_RAS_B SSTL12_DCI L8 RAS_B/A16 U60-U62

AF17 DDR4_BA0 SSTL12_DCI N2 BA0 U60-U62

AL15 DDR4_BA1 SSTL12_DCI N8 BA1 U60-U62

AG15 DDR4_BG0 SSTL12_DCI M2 BG0 U60-U62

AH14 DDR4_ACT_B SSTL12_DCI L3 ACT_B U60-U62

AH16 DDR4_TEN SSTL12_DCI N9 TEN U60-U62

AJ16 DDR4_ALERT_B SSTL12_DCI P9 ALERT_B U60-U62

AD18 DDR4_PAR SSTL12_DCI T3 PAR U60-U62

AJ18 DDR4_ODT SSTL12_DCI K3 ODT U60-U62

Table 1-4: DDR4 Memory Connections to the FPGA (Cont’d)

FPGA

(U1) Pin

Schematic Net

Name

I/O Standard

Component Memory

Pin # Pin Name Ref. Des.

Loading...

Loading...