VC7222 IBERT Getting Started Guide www.xilinx.com 11

UG971 (v5.0) June 12, 2014

Running the GTH IBERT Demonstration

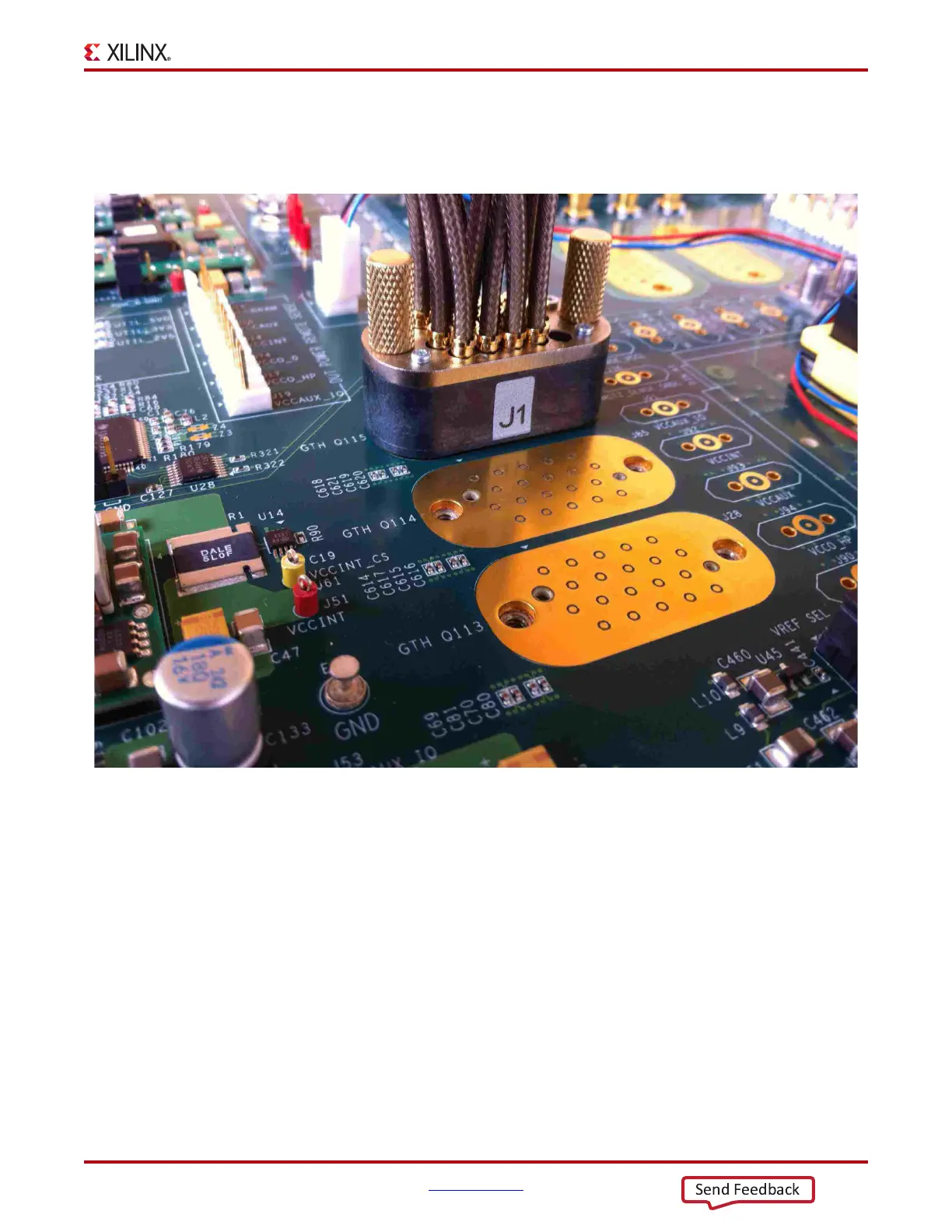

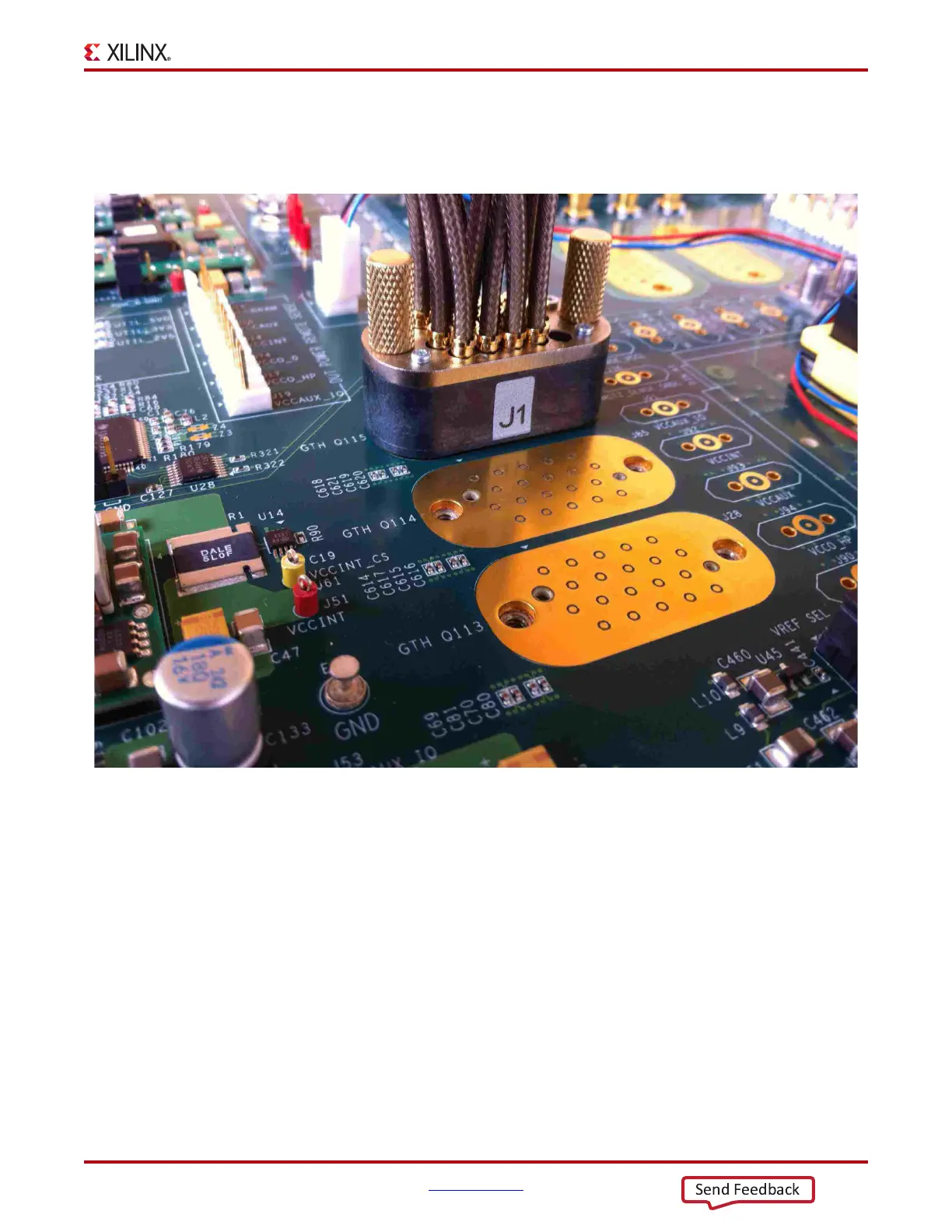

Attach the Samtec BullsEye connector to the GTH Quad 115 (Figure 1-5), aligning the two

indexing pins on the bottom of the connector with the guide holes on the board. Hold the

connector flush with the board and fasten it by tightening the two captive screws.

GTH Transceiver Clock Connections

See Figure 1-2 to identify the P and N coax cables connected to the CLK0 reference clock

inputs. Connect these cables to the SuperClock-2 module as follows:

• CLK0_P coax cable → SMA connector J5 (CLKOUT1_P) on the SuperClock-2 module

• CLK0_N coax cable → SMA connector J6 (CLKOUT1_N) on the SuperClock-2

module

Note:

Any one of the five differential outputs from the SuperClock-2 module can be used to source

the GTH reference clock. CLKOUT1_P and CLKOUT1_N are used here as an example.

X-Ref Target - Figure 1-5

Figure 1-5: BullsEye Connector Attached to GTH Quad 115

Loading...

Loading...