28 www.xilinx.com VC7222 IBERT Getting Started Guide

UG971 (v5.0) June 12, 2014

Chapter 1: VC7222 IBERT Getting Started Guide

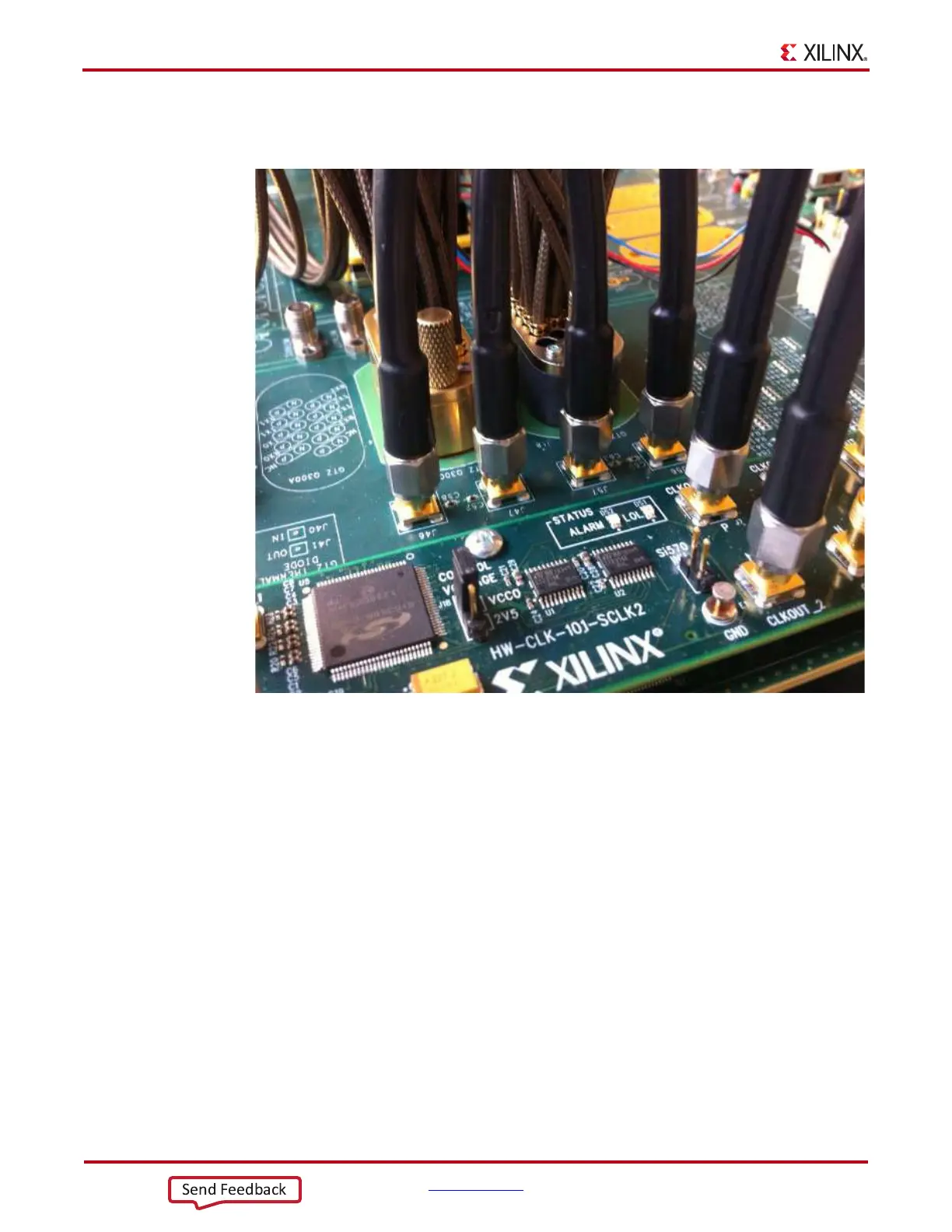

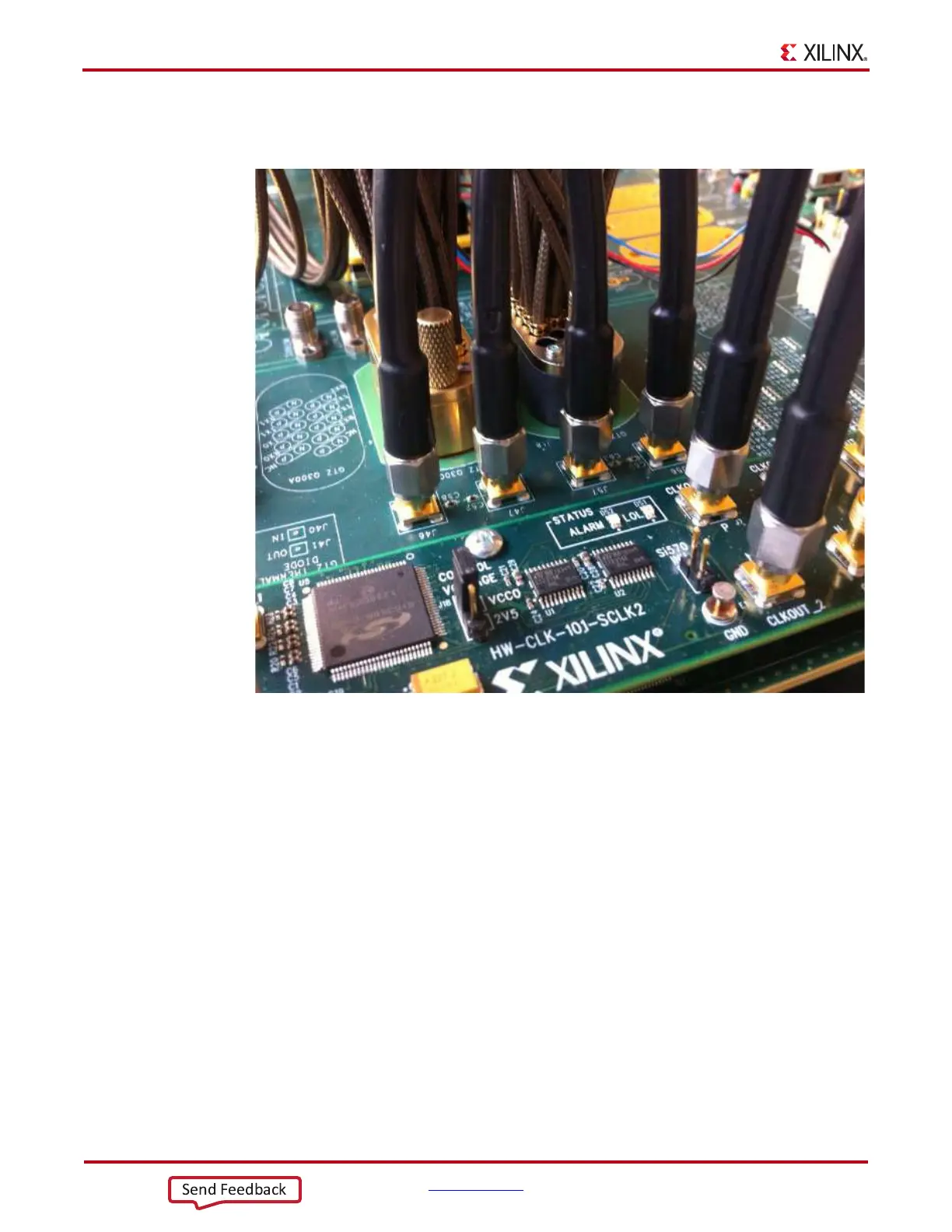

Note: Any one of the five differential outputs from the SuperClock-2 module can be used to source

the GTZ reference clocks. CLKOUT1 and CLKOUT2 are used here as an example.

GTZ TX/RX Loopback Connections

See Figure 1-21 to identify the location of the P and N pins of the GTZ transmitters and

receivers lanes. Use eight SMA female-to-female (F-F) adapters (Figure 1-6) to connect the

transmit and receive cables as shown in Figure 1-7 and detailed in the following list:

•TX0_P→ SMA F-F Adapter → RX0_P

•TX0_N→ SMA F-F Adapter → RX0_N

•TX1_P→ SMA F-F Adapter → RX1_P

•TX1_N→ SMA F-F Adapter → RX1_N

•TX2_P→ SMA F-F Adapter → RX2_P

•TX2_N→ SMA F-F Adapter → RX2_N

•TX3_P→ SMA F-F Adapter → RX3_P

•TX3_N→ SMA F-F Adapter → RX3_N

•TX4_P→ SMA F-F Adapter → RX4_P

•TX4_N→ SMA F-F Adapter → RX4_N

X-Ref Target - Figure 1-23

Figure 1-23: GTZ CLK0 and CLK1 Connection

Loading...

Loading...