VC7222 IBERT Getting Started Guide www.xilinx.com 41

UG971 (v5.0) June 12, 2014

Chapter 2

Creating the GTH IBERT Core

Note: Vivado® Design Suite 2014.2 is required to rebuild the designs shown here.

This section provides a procedure to create a single Quad GTH IBERT core with integrated

SuperClock-2 controller. The procedure assumes Quad 115 and 13.0 Gb/s line rate, but

cores for any of the GTH Quads with any supported line rate can be created following the

same series of steps.

For more details on generating IBERT cores, see the Vivado Design Suite User Guide:

Programming and Debugging (UG908) [Ref 3].

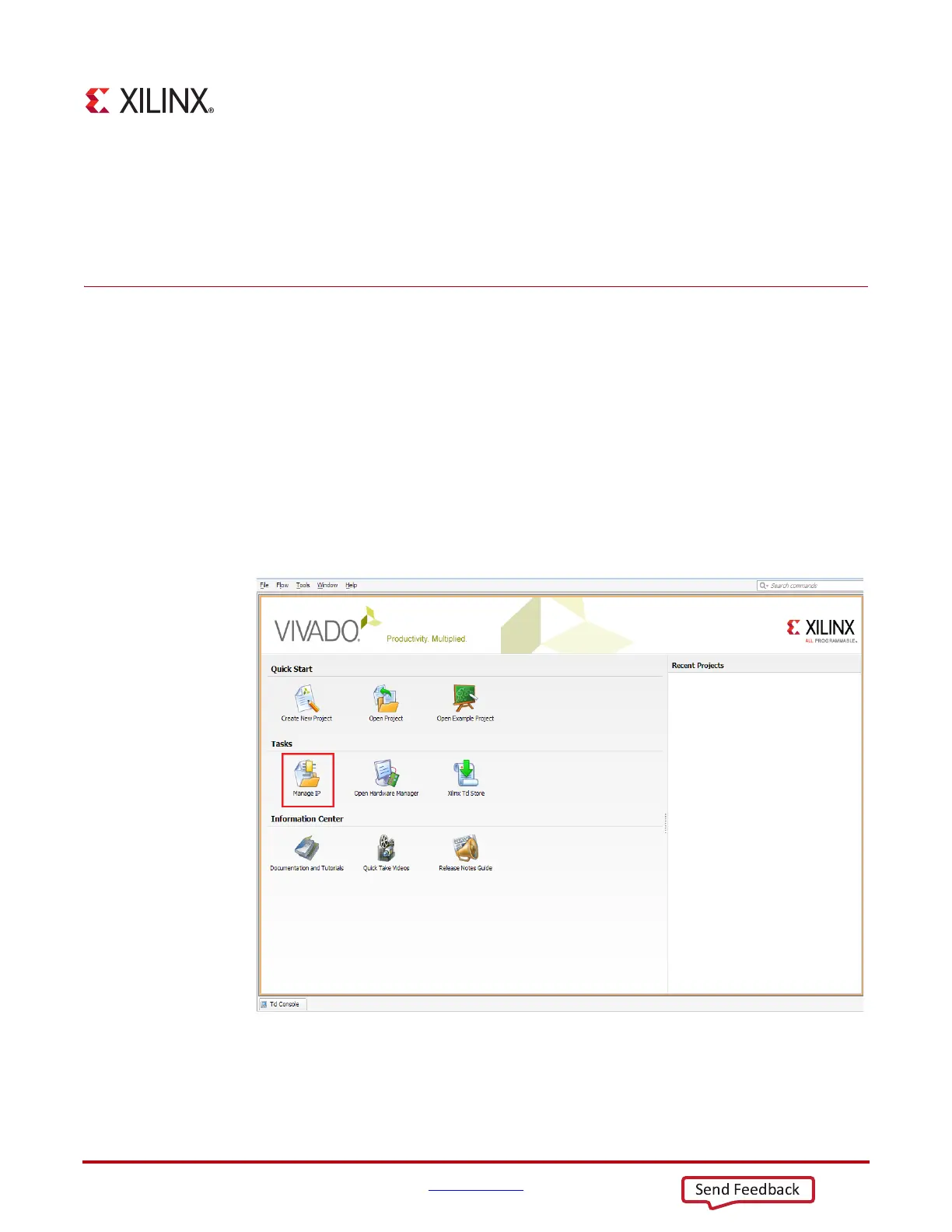

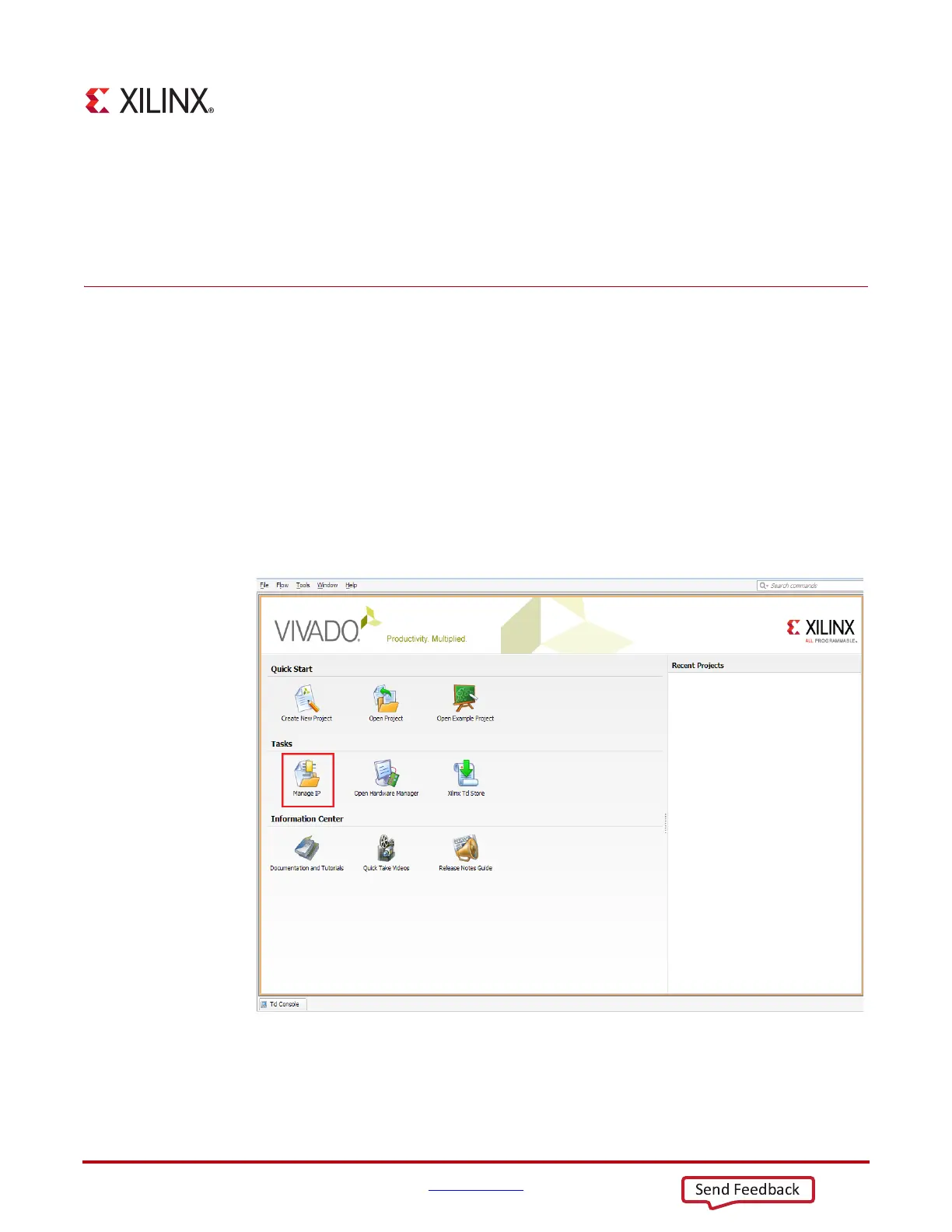

1. Start the Vivado Design Suite.

2. In the Vivado window, click the Manage IP icon highlighted in Figure 2-1, then

select New IP Location.

X-Ref Target - Figure 2-1

Figure 2-1: Initial Window, Vivado Design Suite

Loading...

Loading...