VC7203 GTX Transceiver Characterization Board www.xilinx.com 23

UG957 (v1.3) October 17, 2014

Detailed Description

Information for each GTX transceiver pin is shown in Table 1-13.

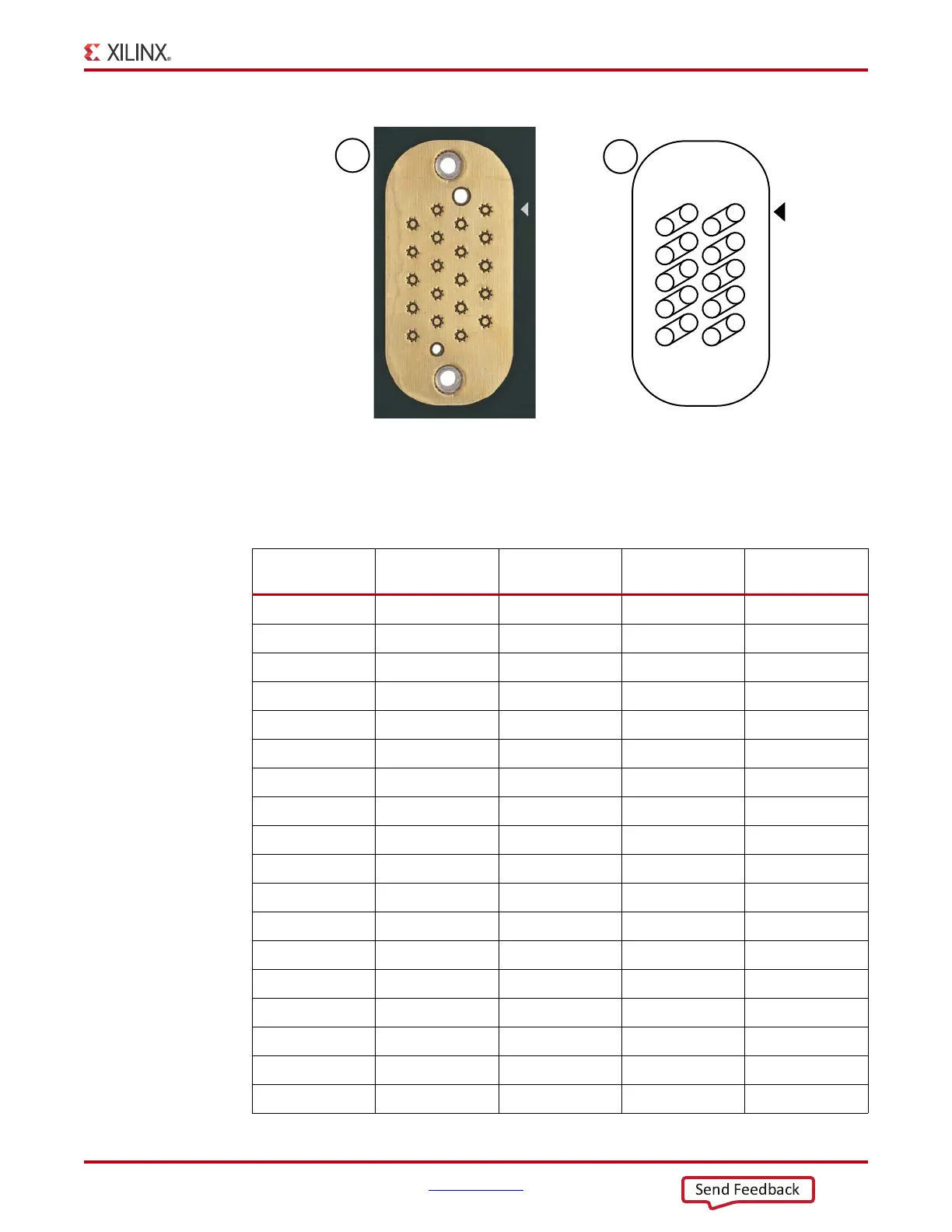

X-Ref Target - Figure 1-11

Figure 1-11: A – GTX Connector Pad. B – GTX Connector Pinout

Table 1-13: GTX Transceiver Pins

U1 FPGA Pin Net Name Quad Connector

Trace Length

(mils)

BB4 111_TX0_P 111 J84 1,929

BB3 111_TX0_N 111 J84 1,929

BB8 111_RX0_P 111 J84 2,149

BB7 111_RX0_N 111 J84 2,148

BA2 111_TX1_P 111 J84 1,808

BA1 111_TX1_N 111 J84 1,808

BA6 111_RX1_P 111 J84 1,855

BA5 111_RX1_N 111 J84 1,855

AY4 111_TX2_P 111 J84 2,097

AY3 111_TX2_N 111 J84 2,097

AY8 111_RX2_P 111 J84 2,101

AY7 111_RX2_N 111 J84 2,100

AW2 111_TX3_P 111 J84 2,650

AW1 111_TX3_N 111 J84 2,650

AW6 111_RX3_P 111 J84 2,533

AW5 111_RX3_N 111 J84 2,532

AV4 112_TX0_P 112 J85 2,692

AV3 112_TX0_N 112 J85 2,692

UG957_c1_11_100712

B

GTX

GTX Connector Pinout

P

P

P

P

P

P

P

P

P

P

N

N

N

N

N

N

N

N

N

N

RX1

TX1

TX2

RX2

TX0

CLK1

RX3

TX3

CLK0

RX0

A

GTX Connector Pad

Loading...

Loading...