VC7203 GTX Transceiver Characterization Board www.xilinx.com 21

UG957 (v1.3) October 17, 2014

Detailed Description

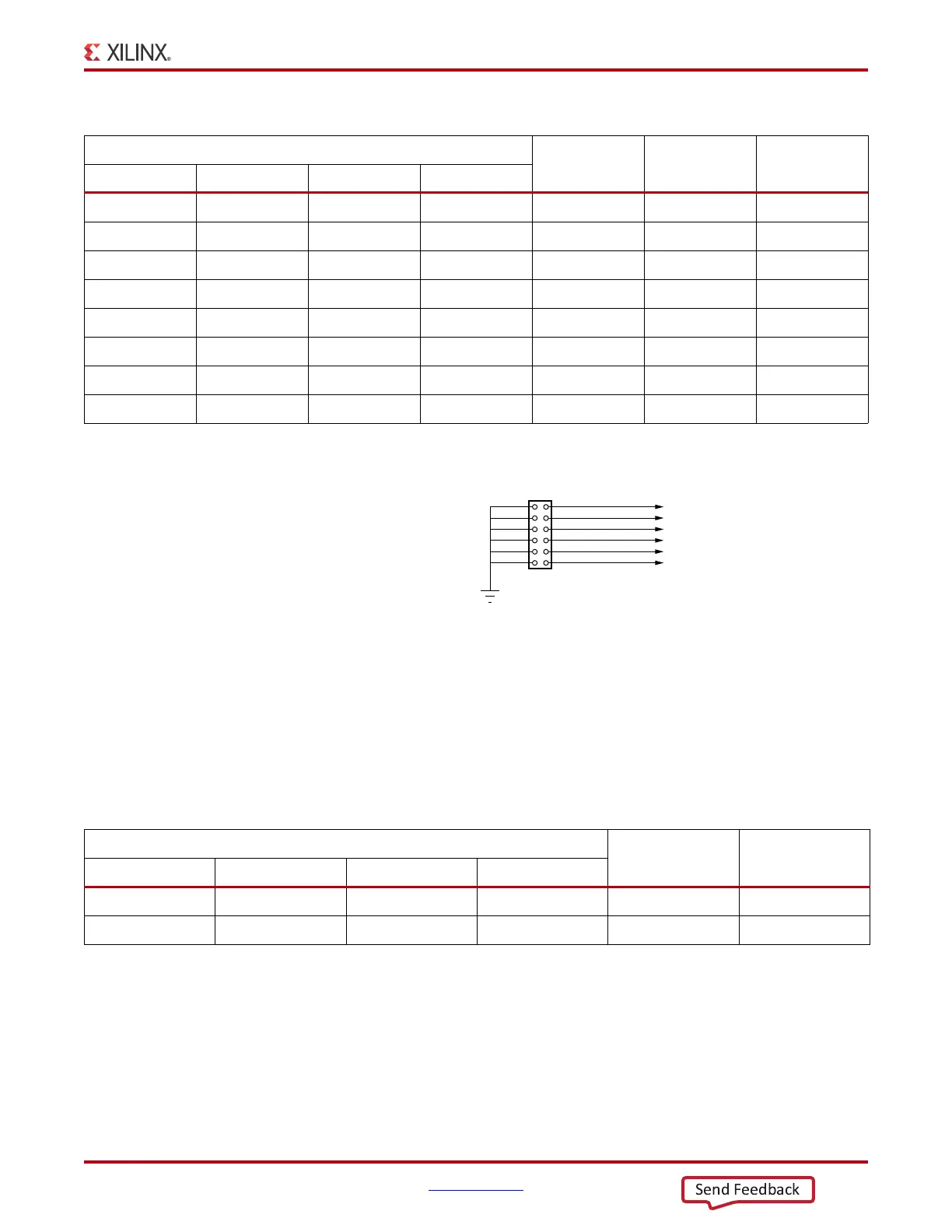

Figure 1-9 shows the user test I/O connector J125 (callout 26, Figure 1-2).

User Pushbuttons (Active-High)

Callout 24, Figure 1-2.

SW4 and SW5 are active-High user pushbuttons that are connected to user I/O pins on the

FPGA as shown in Table 1-12. These switches can be used for any purpose determined by

the user.

Table 1-11: User DIP Switches

FPGA (U1)

Schematic Net

Name

SW2 DIP

Switch Pin

J125 Test

Header Pin

Pin Function Direction I/O Standard

E42 User Switch Input LVCMOS18 USER_SW1 1 2

C40 User Switch Input LVCMOS18 USER_SW2 2 4

C41 User Switch Input LVCMOS18 USER_SW3 3 6

H40 User Switch Input LVCMOS18 USER_SW4 4 8

H41 User Switch Input LVCMOS18 USER_SW5 5 10

H39 User Switch Input LVCMOS18 USER_SW6 6 12

G39 User Switch Input LVCMOS18 USER_SW7 7 —

G41 User Switch Input LVCMOS18 USER_SW8 8 —

X-Ref Target - Figure 1-9

Figure 1-9: User Test I/O

UG932_C1_09_100712

USER_SW1

9

87

65

43

2

10

1

1211

J125

GND

USER_SW2

USER_SW3

USER_SW4

USER_SW5

USER_SW6

Table 1-12: User Pushbuttons

FPGA (U1)

Schematic Net

Name

Reference

Designator

Pin Function Direction I/O Standard

P41 User Pushbutton Input LVCMOS18 USER_PB1 SW5

N41 User Pushbutton Input LVCMOS18 USER_PB2 SW4

Loading...

Loading...