RFSoC Data Converter Evaluation Tool User Guide 32

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 4: Clocking

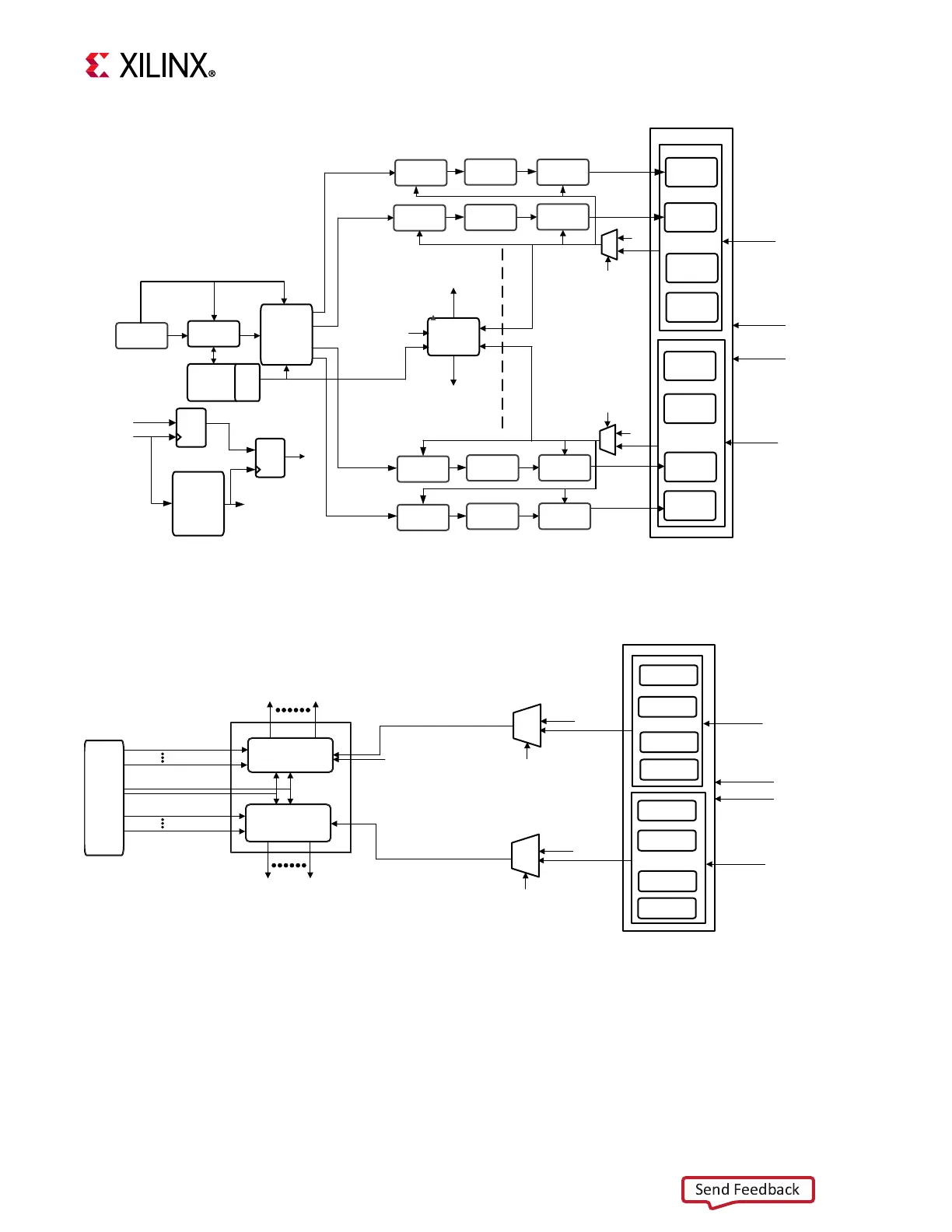

X-Ref Target - Figure 4-7

Figure 4-7: RF-DAC Multi-Tile Sync Clocking Structure

DAC 2

DAC 3

PL DDR

+ MIG

DMA

Stream

Mux

DAC 4

DAC 5

DAC 6

DAC 7

333 MHz

DAC 0 Analog Clock (PCB)

DAC 1 Analog Clock (PCB)

SYSREF (PCB)

PL SYSREF (PCB)

PL REF CLK (PCB)

MMCM

PL CLK

(Fabric

Clock)

User_sysref_dac

User_sysref_dac

(Fabric Clock)

PL CLK

Example:

Fs = 6.4 GHz

Interpolation = x1

SYREF = 8 MHz

PL SYSREF = 8 MHz

PL REF CLK = 200 MHz

Tile0 _DAC_

Clock out

Tile 0

Tile 1

PS

GP

IO

Sync

logic

To Tile0

channels

Multi-Tile Control

PL CLK = 400 MHz

Clock

Converter

Clock

Converter

Loopback

Component

Loopback

Component

AXIS FIFO

64 KS

AXIS FIFO

64 KS

Clock

Converter

Loopback

Component

AXIS FIFO

64 KS

Clock

Converter

Loopback

Component

AXIS FIFO

64 KS

To Tile1

channels

PL CLK

Tile1 _DAC_

Clock out

Multi-Tile Control

DAC 0

DAC 1

PL CLK

X21250-092118

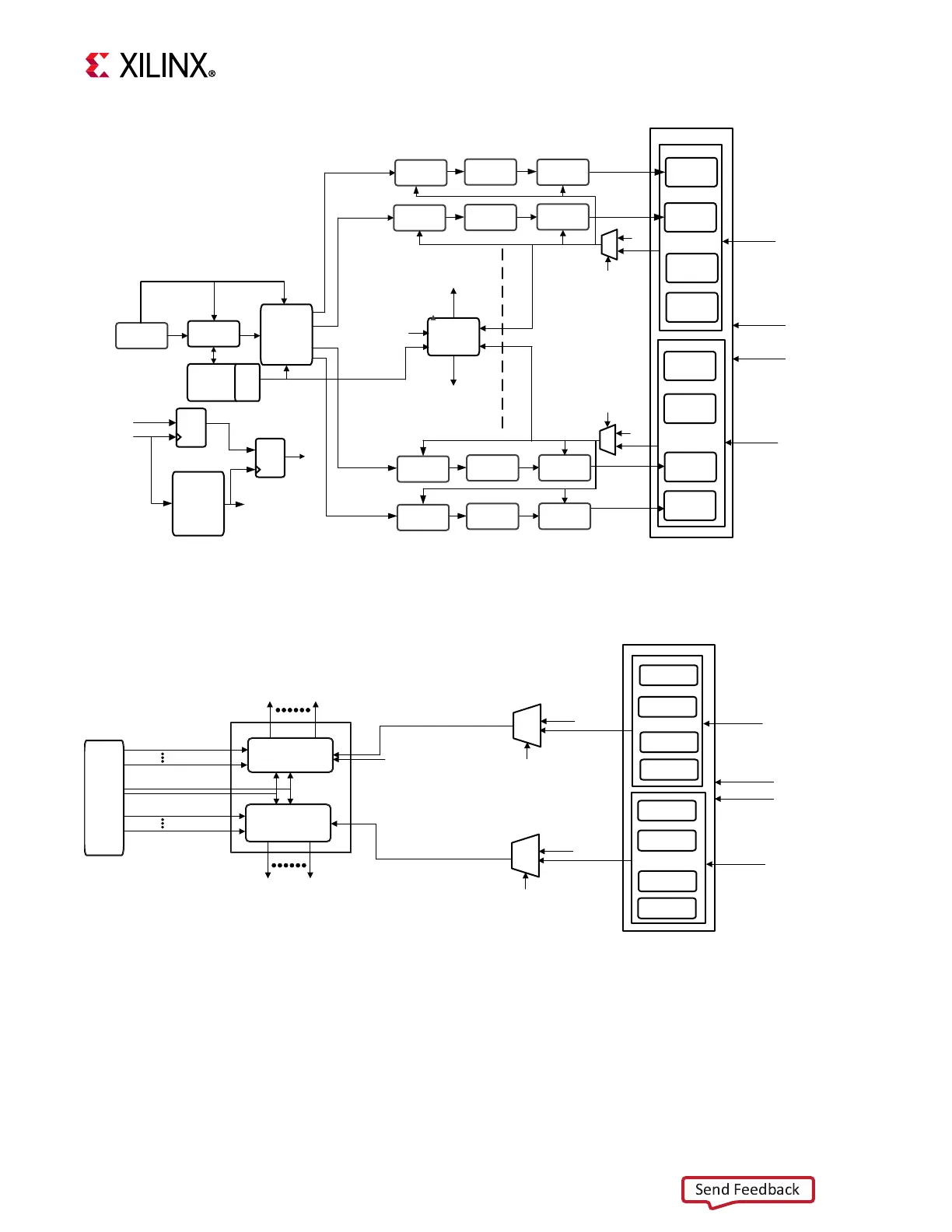

X-Ref Target - Figure 4-8if

Figure 4-8: RF-DAC Control Signals for Multi-Tile Sync (Sync Block)

DAC 2

DAC 3

DAC 4

DAC 5

DAC 6

DAC 7

DAC 0 Analog Clock (PCB)

DAC 1 Analog Clock (PCB)

SYSREF (PCB)

User_sysref_dac (Fabric Clock)

PL CLK

Tile0 _DAC_Clock out

Tile 0

Tile 1

Multi-Tile Control

DAC 0

DAC 1

N-stage

Sync logic

PS

GPIO

Channel 5-6 Control

N-stage

Sync logic

PS Clock

DAC 0 to DAC 3

DAC 4 to DAC 7

Tile0 _clk

Tile1 _clk

Multi-Tile Control

Channel 0-4 Control

PL CLK

BUFG

MUX

PL CLK

Tile0 _DAC_Clock out

Multi-Tile Control

BUFG

MUX

X21251-092118

Loading...

Loading...