RFSoC Data Converter Evaluation Tool User Guide 33

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 4: Clocking

Table 4-2 lists the clocks used for RF-DAC control path and datapath.

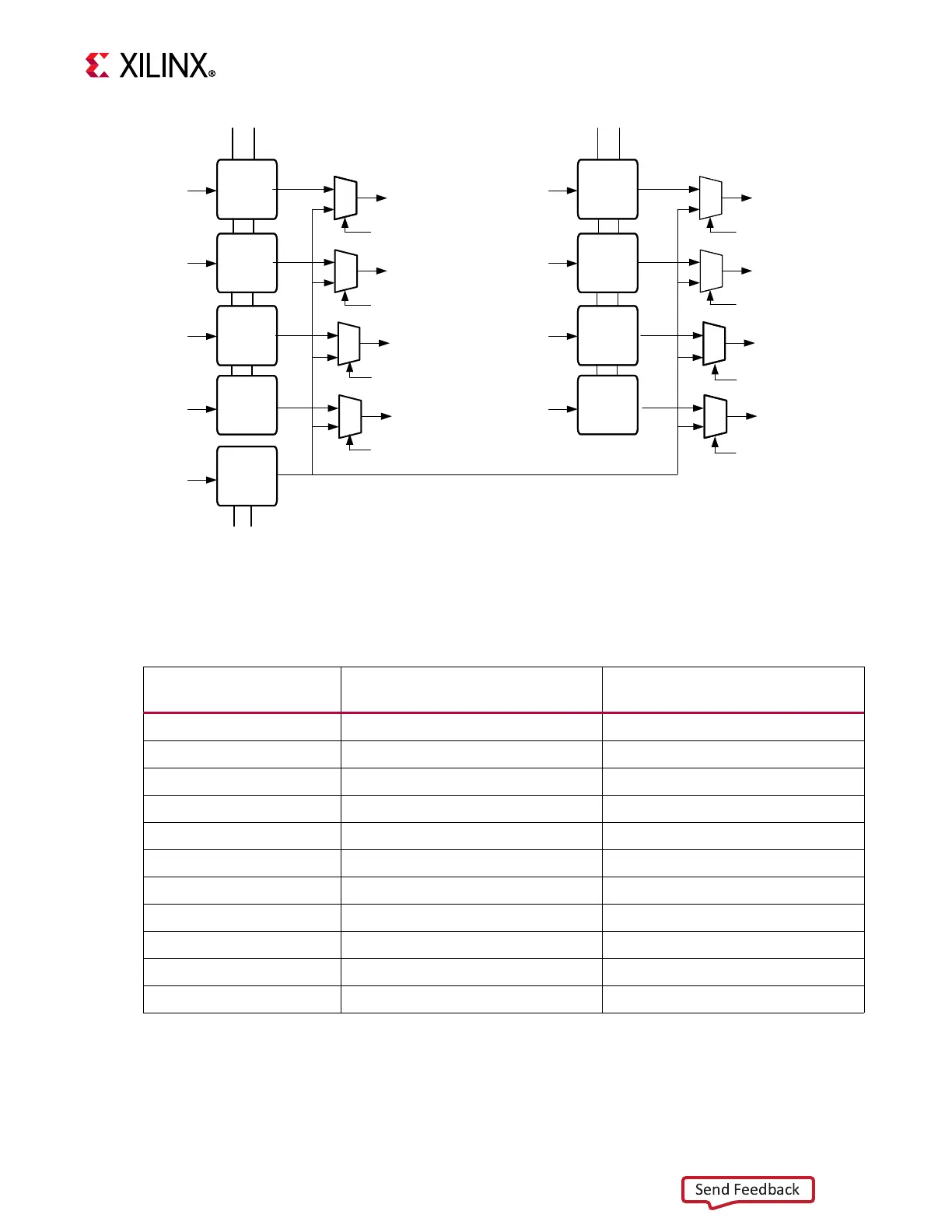

X-Ref Target - Figure 4-9

Figure 4-9: N-Stage Sync Logic for RF-DAC

Synchronizer

Channel 0 Control

Channel 1 Control

Channel 2 Control

Channel 3 Control

Synchronizer

Synchronizer

Synchronizer

Channel 0 Control

Synchronizer

Tile0 _clk

PS Clock

PL CLK

PS Clock

Multi-Tile Control

DAC 0 CONTROL

Multi-Tile Control

DAC 1 CONTROL

Multi-Tile Control

DAC 2 CONTROL

Multi-Tile Control

DAC 3 CONTROL

Synchronizer

Channel 4 Control

Channel 5 Control

Channel 6 Control

Channel 7 Control

Synchronizer

Synchronizer

Synchronizer

Tile1 _clk

PS Clock

Multi-Tile Control

DAC 4 CONTROL

Multi-Tile Control

DAC 5 CONTROL

Multi-Tile Control

DAC 6 CONTROL

Multi-Tile Control

DAC 7 CONTROL

X21252-090918

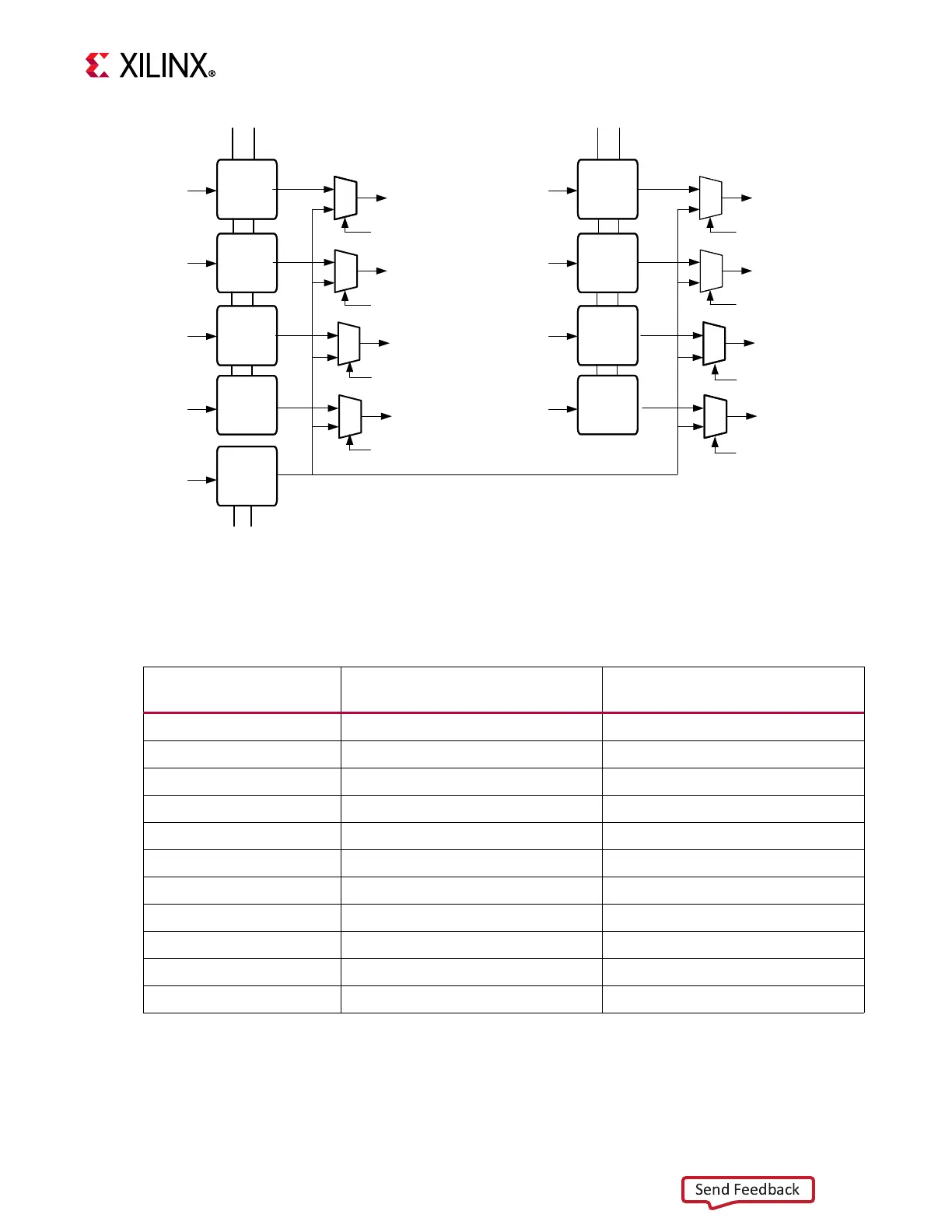

Table 4-2: Clock Domains in RF-DAC Control and Datapath

Logic Block

Clock Domain

(300 MHz)

DAC_CLK_OUT

(409.625 MHz)

PL DDR MIG X

SG DMA X

Streaming MUX X

Memory Loopback 0 x (Write) x (Read)

Memory Loopback 1 x (Write) x (Read)

Memory Loopback 2 x (Write) x (Read)

Memory Loopback 3 x (Write) x (Read)

Memory Loopback 4 x (Write) x (Read)

Memory Loopback 5 x (Write) x (Read)

Memory Loopback 6 x (Write) x (Read)

Memory Loopback 7 x (Write) x (Read)

Loading...

Loading...