KINTEX UltraScale+ FPGA Board AXKU040 User Manual

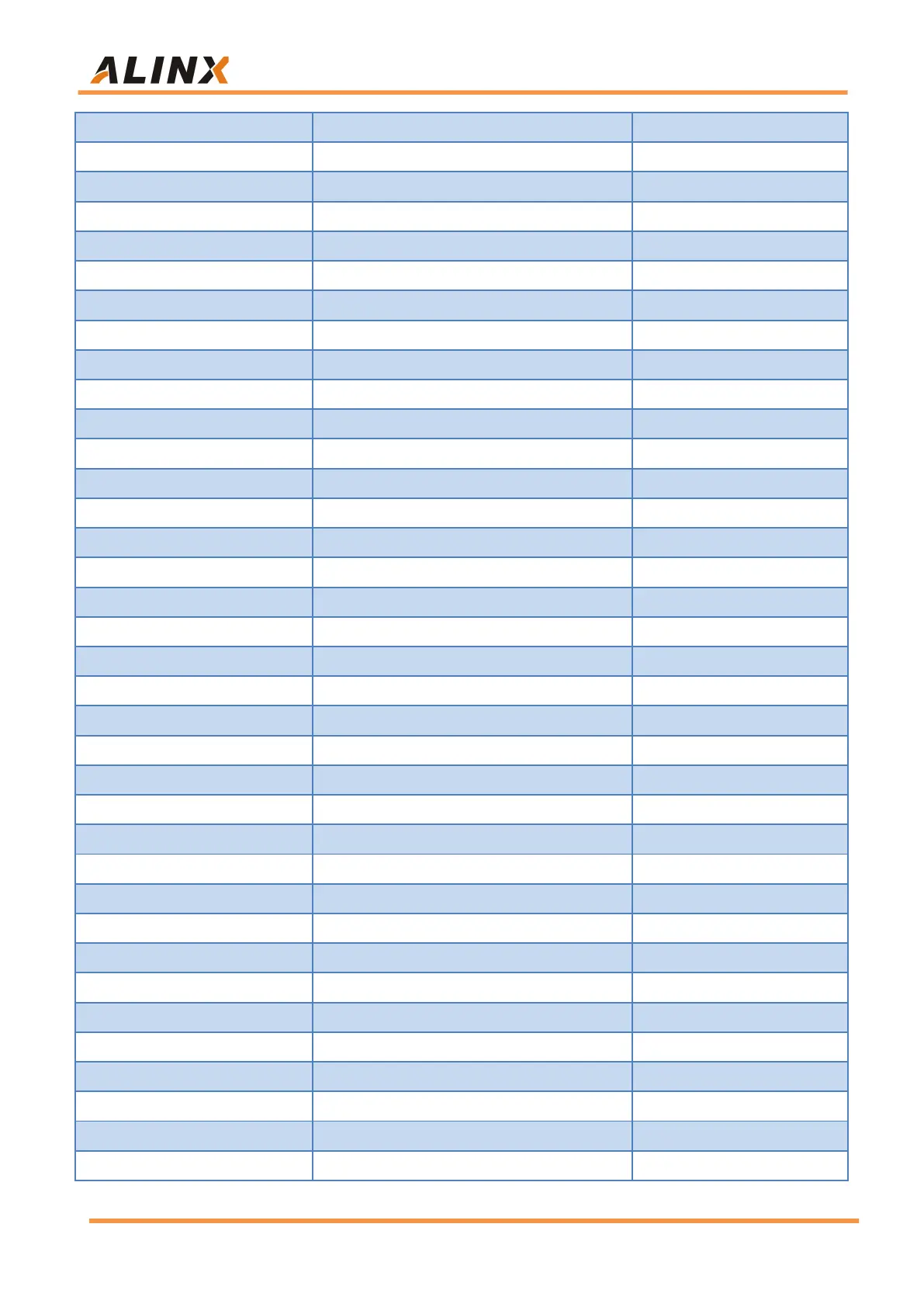

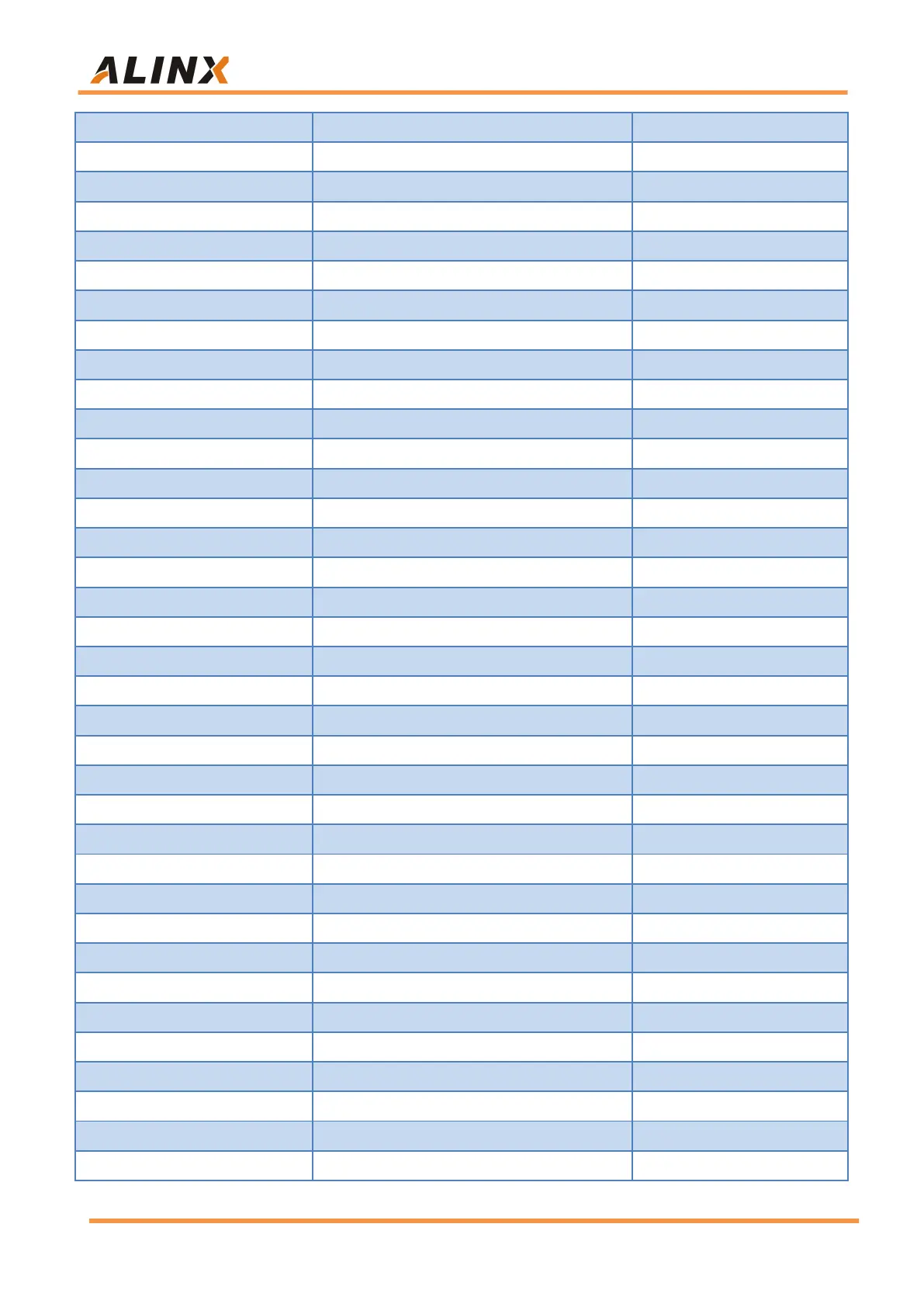

IO_L19P_T3L_N0_DBC_AD9P_46

IO_L4P_T0U_N6_DBC_AD7P_44

IO_L4N_T0U_N7_DBC_AD7N_44

IO_L10P_T1U_N6_QBC_AD4P_44

IO_L10N_T1U_N7_QBC_AD4N_44

IO_L16P_T2U_N6_QBC_AD3P_44

IO_L16N_T2U_N7_QBC_AD3N_44

IO_L22P_T3U_N6_DBC_AD0P_44

IO_L22N_T3U_N7_DBC_AD0N_44

IO_L4P_T0U_N6_DBC_AD7P_46

IO_L4N_T0U_N7_DBC_AD7N_46

IO_L10P_T1U_N6_QBC_AD4P_46

IO_L10N_T1U_N7_QBC_AD4N_46

IO_L16P_T2U_N6_QBC_AD3P_46

IO_L16N_T2U_N7_QBC_AD3N_46

IO_L22P_T3U_N6_DBC_AD0P_46

IO_L22N_T3U_N7_DBC_AD0N_46

IO_L16N_T2U_N7_QBC_AD3N_45

IO_L19N_T3L_N1_DBC_AD9N_45

IO_L19P_T3L_N0_DBC_AD9P_45

IO_L10N_T1U_N7_QBC_AD4N_45

IO_L10P_T1U_N6_QBC_AD4P_45

IO_L16P_T2U_N6_QBC_AD3P_45

Loading...

Loading...