Chapter 4: Development Board Setup 4–5

Factory Default Switch and Jumper Settings

May 2013 Altera Corporation Cyclone V SoC Development Kit

User Guide

4. Set the following jumper blocks to match Table 4–4 and Figure 4–1.

For more information about the FPGA board settings, refer to the Cyclone V SoC

Development Board Reference Manual.

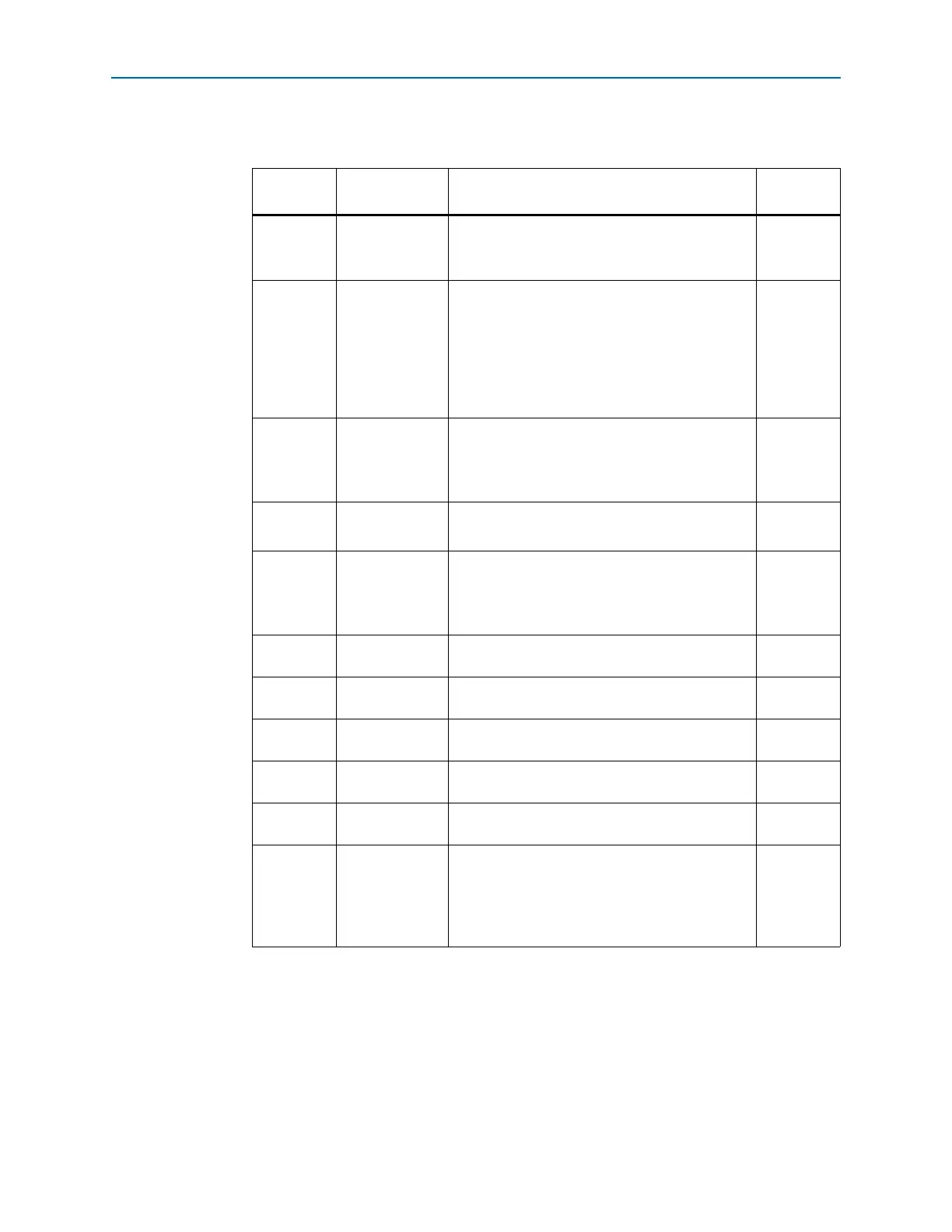

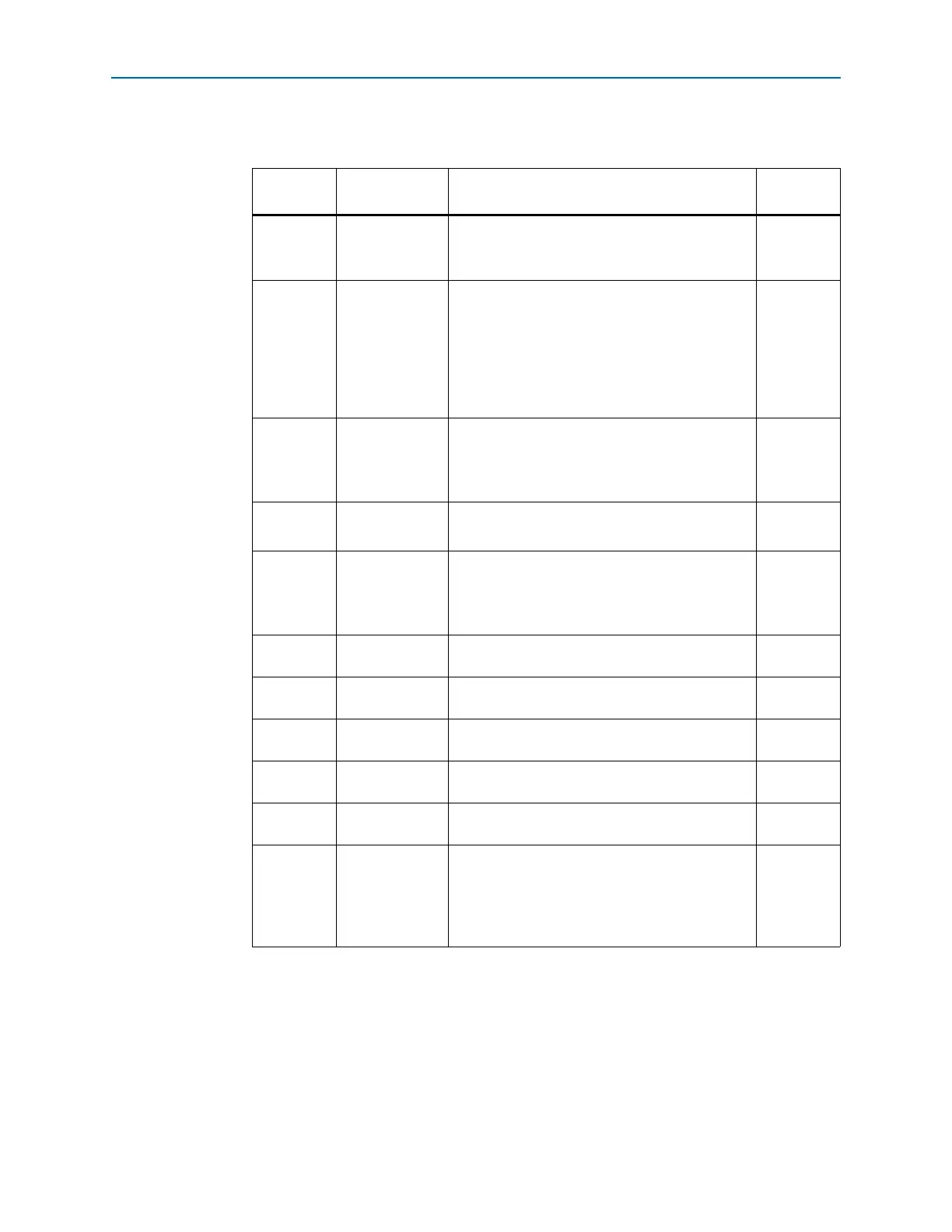

Table 4–4. Default Jumper Settings

Board

Reference

Board Label Description

Default

Position

J5 9V

■ SHORT: Powers the flash memory device.

■ OPEN: Executes a fast write to the flash

contents.

OPEN

J6 JTAG HPS SEL

■ SHORT: Controls the HPS from On-Board USB

Blaster II JTAG master.

■ OPEN: Controls the HPS from MICTOR-based

JTAG master, such as DSTREAM or Lauterbach

programming cables. Also, sets SW4.1 to ON to

remove the On-Board USB Blaster II from

driving the HPS JTAG input port in this mode.

SHORT

J7 JTAG SEL

■ SHORT: The USB Blaster II is the source of the

JTAG chain.

■ OPEN: The Mictor is the source of the JTAG

chain.

SHORT

J13 OSC1_CLK_SEL

■ SHORT: Selects the on board 25MHz clock.

■ OPEN: Selects SMA.

SHORT

J16 JTAG MIC SEL

■ SHORT: JTAG TRST input to HPS driven from

the JTAG chain.

■ OPEN: JTAG TRST input to HPS driven from the

MICTOR.

OPEN

J26 CLKSEL0 Selects the HPS clock settings.

(

1

)

SHORT pins

2-3

J27 CLKSEL1 Selects the HPS clock settings.

(

1

)

SHORT pins

2-3

J28 BOOTSEL0 Selects the boot mode and source for the HPS.

(

1

)

SHORT pins

2-3

J29 BOOTSEL1 Selects the boot mode and source for the HPS.

(

1

)

SHORT pins

2-3

J30 BOOTSEL2 Selects the boot mode and source for the HPS.

(

1

)

SHORT pins

1-2

J31 SPI I2C

■ SHORT: Select SPI bus access from HPS to

Linear Tech daughter card interface through

J32.

■ OPEN: Select I

2

C bus access from HPS to Linear

Tech daughter card interface through J32.

OPEN

Note to Table 4–4:

(1) For more information, refer to the Cyclone V Device Handbook.

Loading...

Loading...