249

8025I–AVR–02/09

ATmega48P/88P/168P/328P

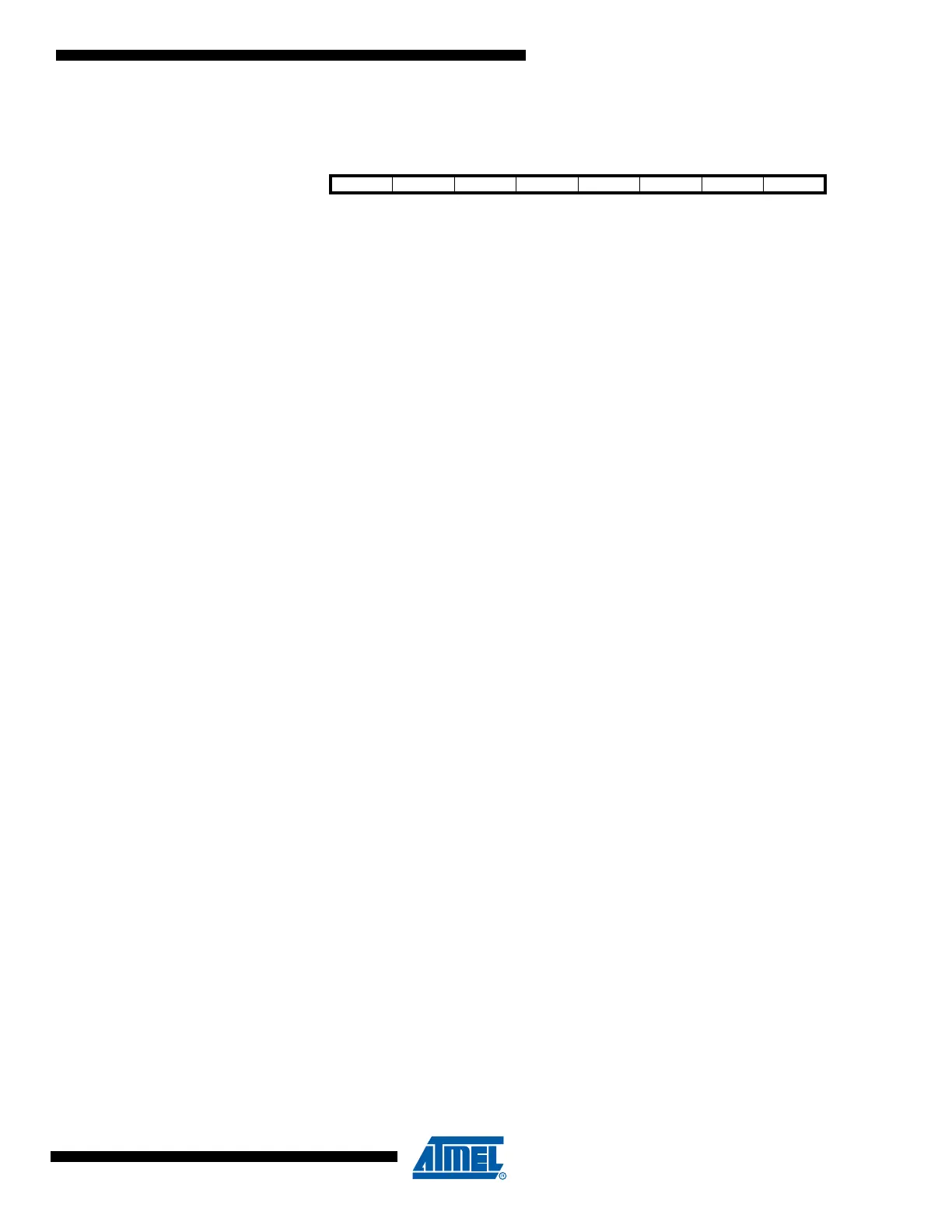

20.3.3 DIDR1 – Digital Input Disable Register 1

• Bit 7..2 – Res: Reserved Bits

These bits are unused bits in the ATmega48P/88P/168P/328P, and will always read as zero.

• Bit 1, 0 – AIN1D, AIN0D: AIN1, AIN0 Digital Input Disable

When this bit is written logic one, the digital input buffer on the AIN1/0 pin is disabled. The corre-

sponding PIN Register bit will always read as zero when this bit is set. When an analog signal is

applied to the AIN1/0 pin and the digital input from this pin is not needed, this bit should be writ-

ten logic one to reduce power consumption in the digital input buffer.

Bit 76543210

(0x7F) ––––––AIN1DAIN0DDIDR1

Read/Write RRRRRRR/WR/W

Initial Value 00000000

Loading...

Loading...