104

8025I–AVR–02/09

ATmega48P/88P/168P/328P

symmetry around BOTTOM the OCnx value at MAX must correspond to the result of an up-

counting Compare Match.

• The timer starts counting from a value higher than the one in OCRnx, and for that reason

misses the Compare Match and hence the OCnx change that would have happened on the

way up.

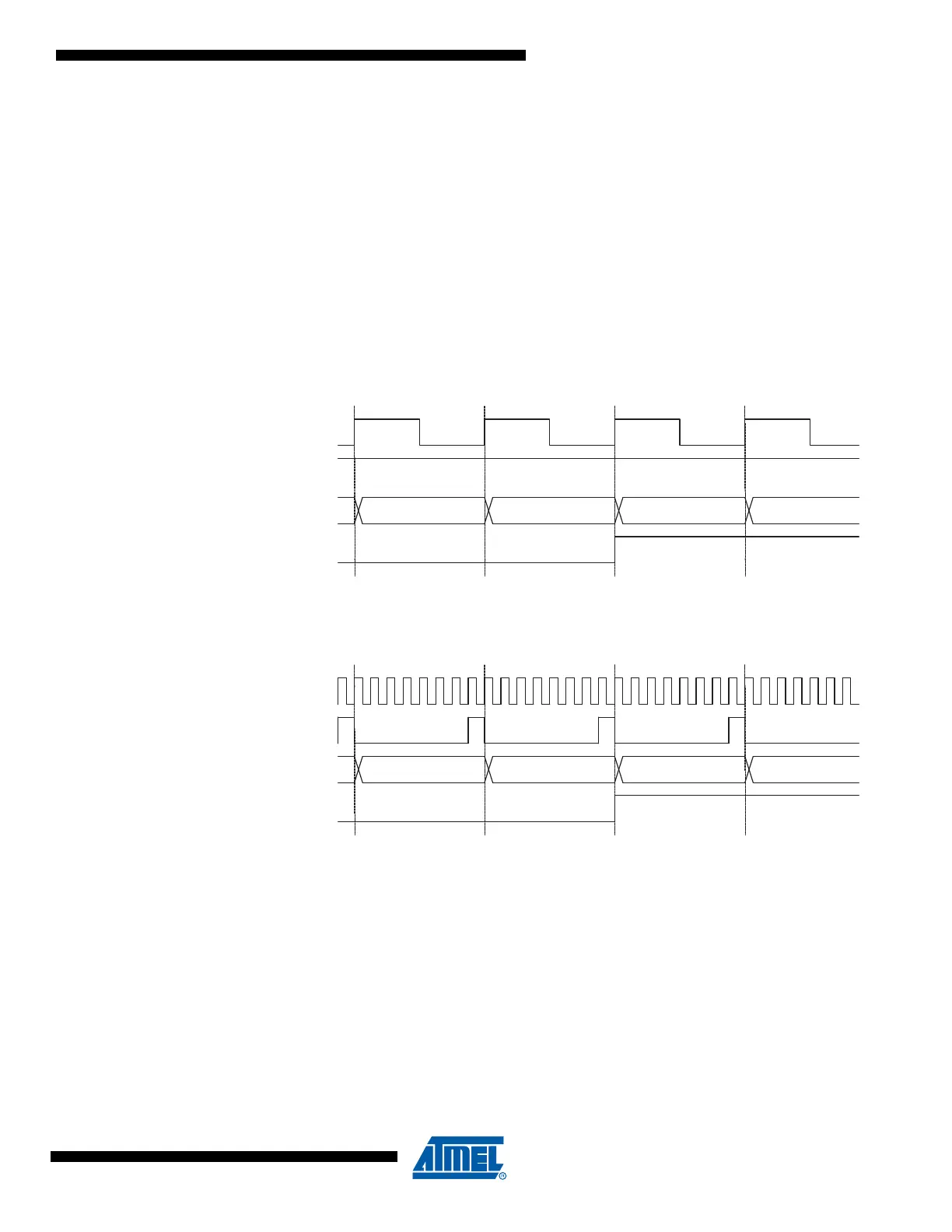

12.8 Timer/Counter Timing Diagrams

The Timer/Counter is a synchronous design and the timer clock (clk

T0

) is therefore shown as a

clock enable signal in the following figures. The figures include information on when interrupt

flags are set. Figure 12-8 contains timing data for basic Timer/Counter operation. The figure

shows the count sequence close to the MAX value in all modes other than phase correct PWM

mode.

Figure 12-8. Timer/Counter Timing Diagram, no Prescaling

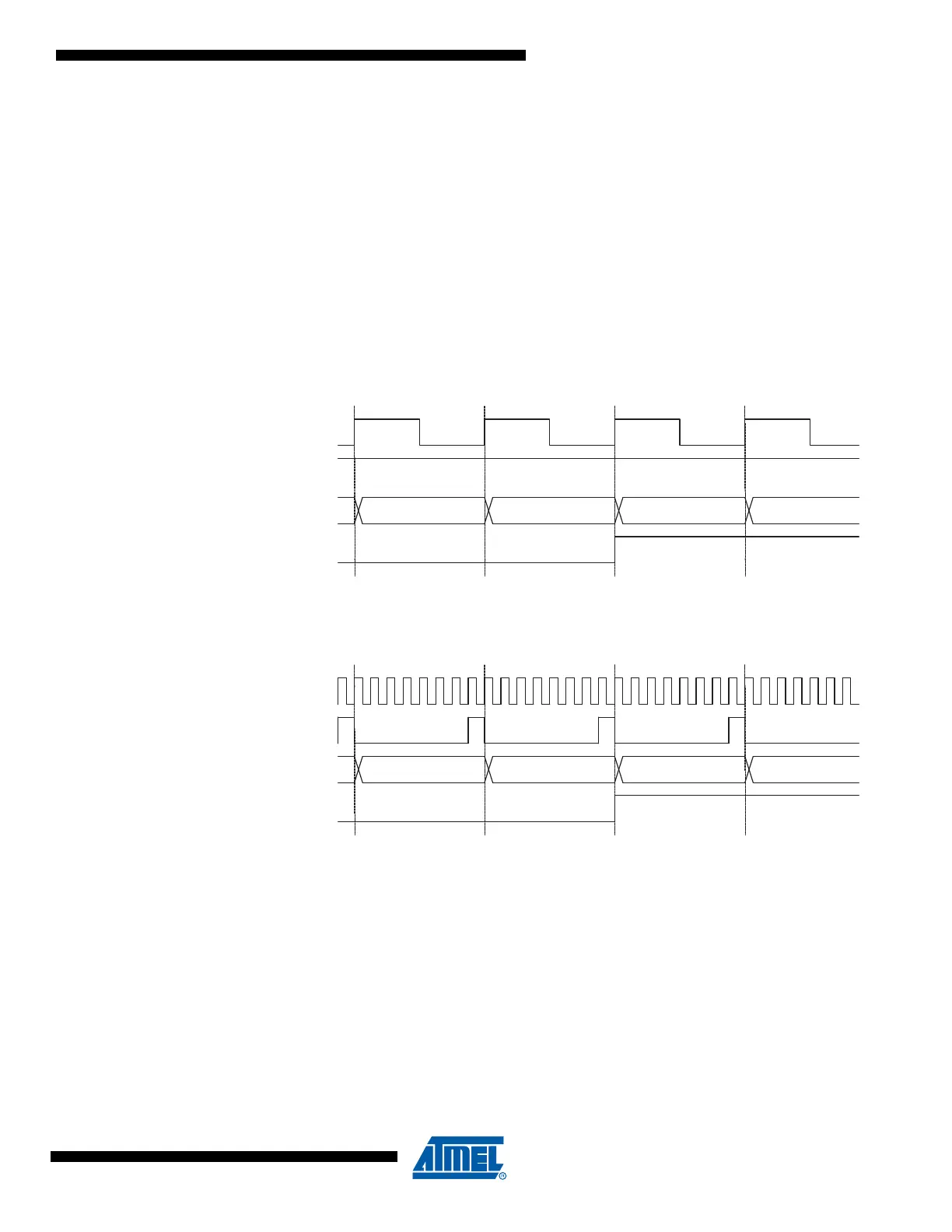

Figure 12-9 shows the same timing data, but with the prescaler enabled.

Figure 12-9. Timer/Counter Timing Diagram, with Prescaler (f

clk_I/O

/8)

Figure 12-10 shows the setting of OCF0B in all modes and OCF0A in all modes except CTC

mode and PWM mode, where OCR0A is TOP.

clk

Tn

(clk

I/O

/1)

TOVn

clk

I/O

TCNTn MAX - 1 MAX BOTTOM BOTTOM + 1

TOVn

TCNTn

MAX - 1 MAX BOTTOM BOTTOM + 1

clk

I/O

clk

Tn

(clk

I/O

/8)

Loading...

Loading...