264

8025I–AVR–02/09

ATmega48P/88P/168P/328P

• Bit 5 – ADATE: ADC Auto Trigger Enable

When this bit is written to one, Auto Triggering of the ADC is enabled. The ADC will start a con-

version on a positive edge of the selected trigger signal. The trigger source is selected by setting

the ADC Trigger Select bits, ADTS in ADCSRB.

• Bit 4 – ADIF: ADC Interrupt Flag

This bit is set when an ADC conversion completes and the Data Registers are updated. The

ADC Conversion Complete Interrupt is executed if the ADIE bit and the I-bit in SREG are set.

ADIF is cleared by hardware when executing the corresponding interrupt handling vector. Alter-

natively, ADIF is cleared by writing a logical one to the flag. Beware that if doing a Read-Modify-

Write on ADCSRA, a pending interrupt can be disabled. This also applies if the SBI and CBI

instructions are used.

• Bit 3 – ADIE: ADC Interrupt Enable

When this bit is written to one and the I-bit in SREG is set, the ADC Conversion Complete Inter-

rupt is activated.

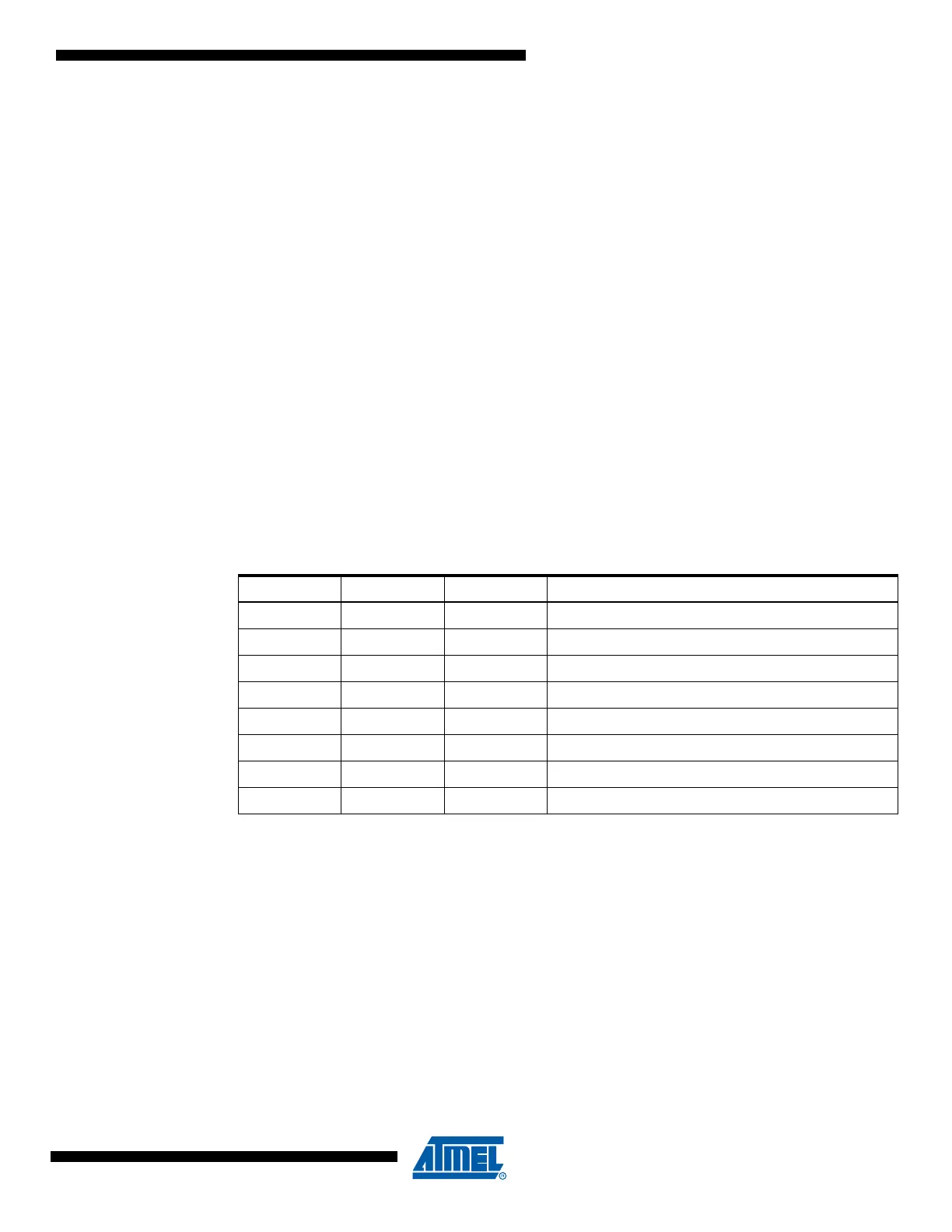

• Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits

These bits determine the division factor between the system clock frequency and the input clock

to the ADC.

Table 21-5. ADC Prescaler Selections

ADPS2 ADPS1 ADPS0 Division Factor

000 2

001 2

010 4

011 8

100 16

101 32

110 64

111 128

Loading...

Loading...