73

! Service Request Enable Register ( SRE )

The Service Request Enable Register that enables or disables (i.e., masks )

corresponding summary messages in the Status Byte Register. The SRE is cleared

at power up. Refer to

“Status Byte Register” for the bit functions.

Use *SRE to write to this register and *SRE? to read this register.

! Standard Event Status Register ( ESR)

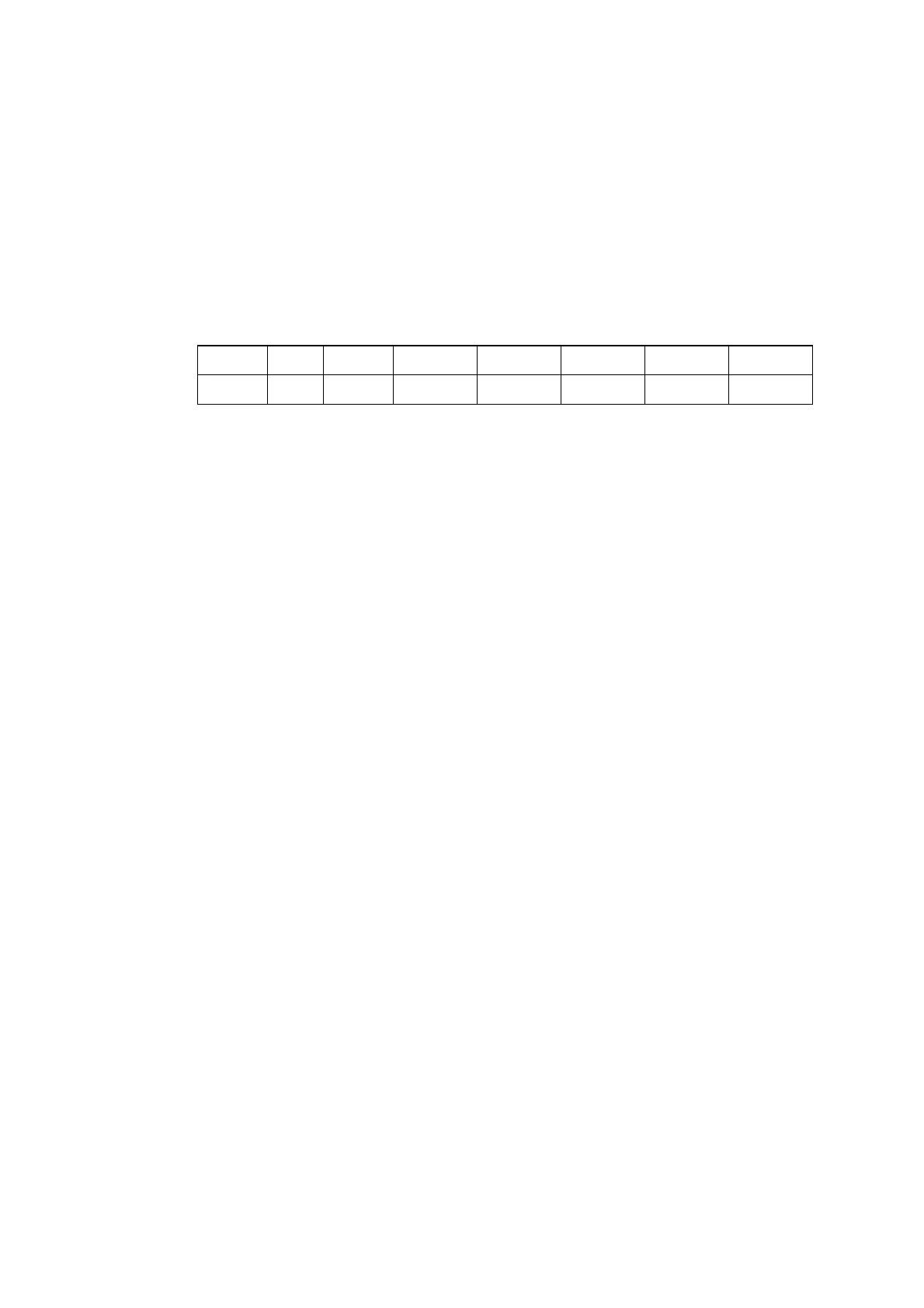

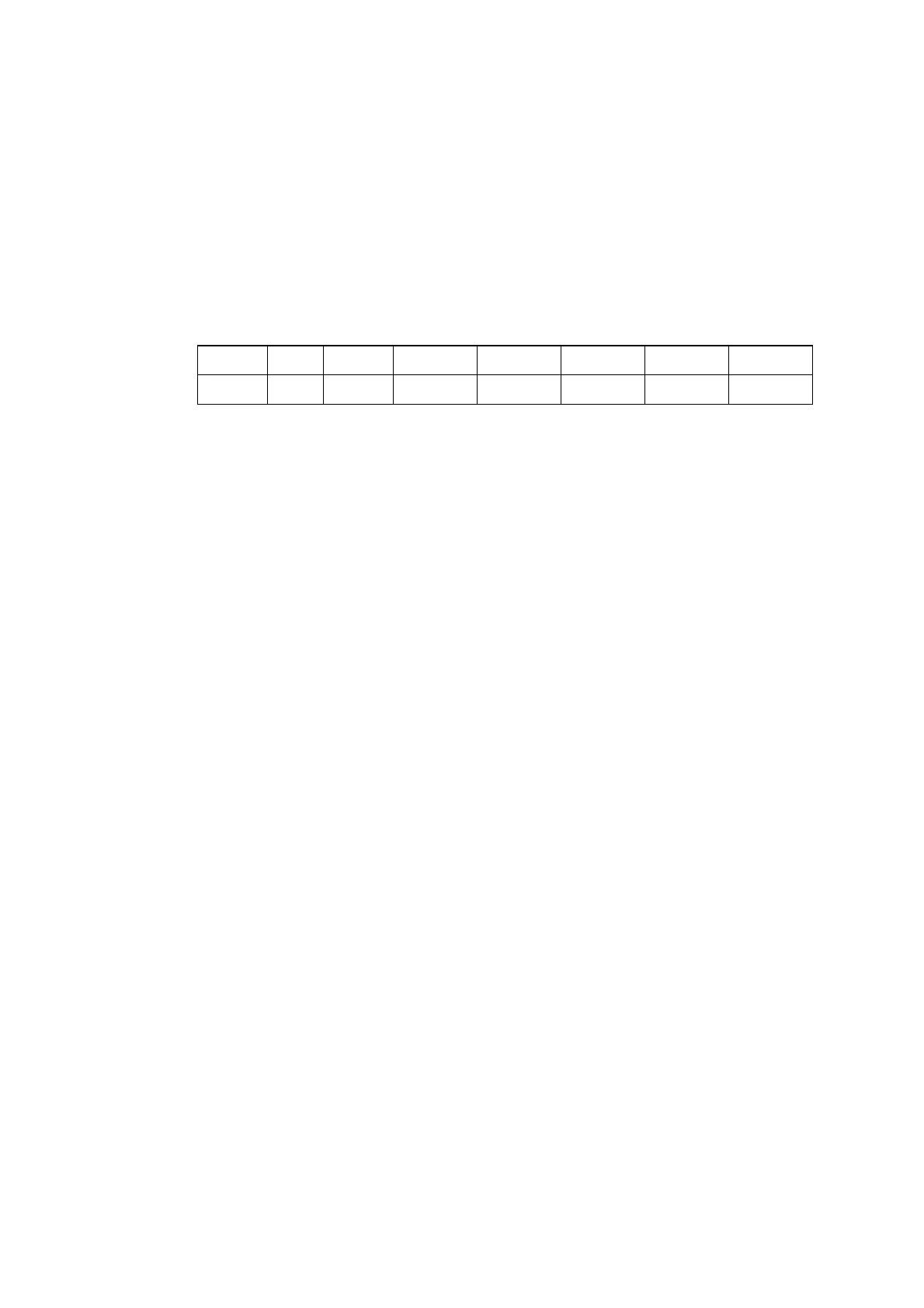

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

PON 0 CME EXE DDE QYE 0 OPC

Bit 0 (OPC) - Operation complete. This bit is generated in response to the *OPC

command and indicates that the interface is ready to accept another

message.

Bit 1 is not used. (Always set to 0 )

Bit 2 (QYE) - Query Error. Attempt has been made to read the Output Queue

when no output is present or pending. Or, both input and output

buffer are full.

Bit 3 (DDE) - Device-Dependent Error. Incorrect input during calibration, or

RS-232 input buffer overflow.

Bit 4 (EXE) - Execution Error. Parameter is wrong or unknown.

Bit 5 (CME) - Command Error. Command is wrong or unknown.

Bit 6 is not used. (Always set to 0)

Bit 7 (PON) - Power On. Power has been cycled off and on since the last time the

ESR was read.

Note: 1. The Standard Event Status Register

can be read by the *ESR? query.

2. The register is cleared at power up or use *ESR? and *CLS commands.

Loading...

Loading...