Electronic Instrumentation

UM3148 – DT5730/DT5725 User Manual rev. 2

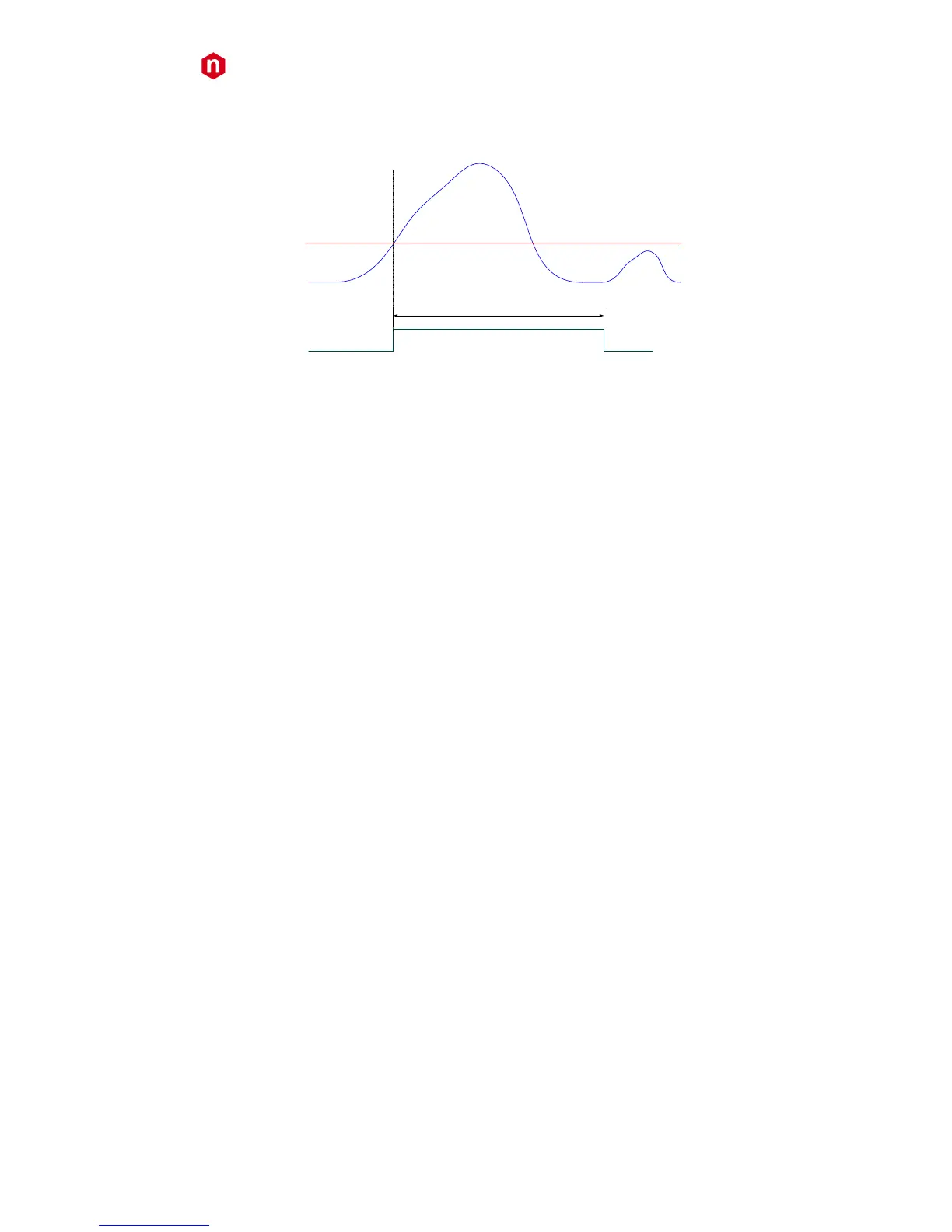

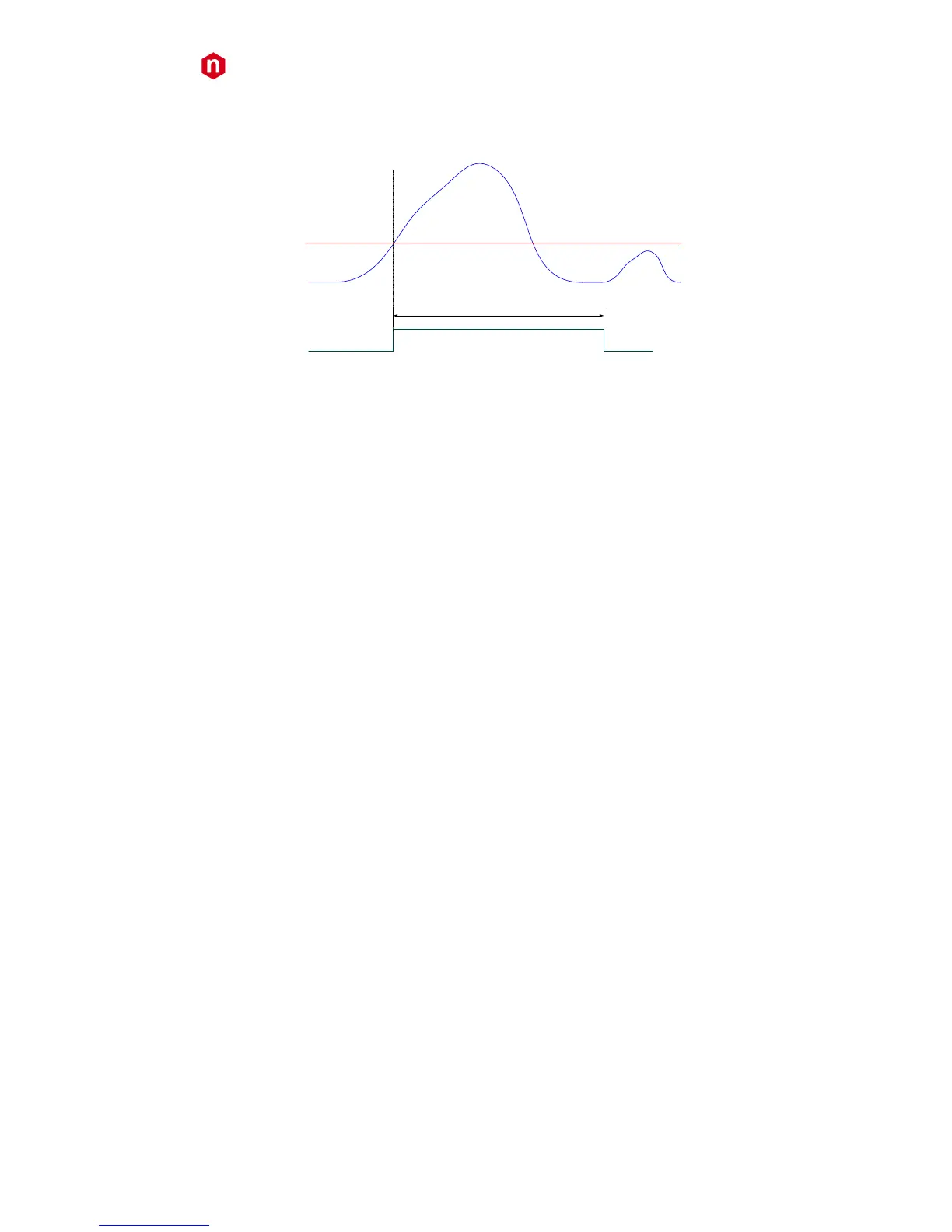

▪ a pulse of configurable width (see Fig. 9.12). The width parameter can be set at register address 0x1n70.

CH0 IN

THRESHOLD

pulse [0]

WIDTH

Fig. 9.12: Channel pulse signal

The FPGA, by register address 0x1n84, can be programmed in order the trigger request for a couple of adjacent

channels to be the

AND,

ONLY CH(n),

ONLY CH(n+1),

OR

of the relevant self-trigger signals (see Fig. 9.10).

Default Conditions: by default, the FPGA is programmed so that the trigger request is the OR of two pulses of 4ns-

width.

Note: the above described configurability of both the self-trigger logic and the trigger request logic are supported only

by AMC FPGA firmware releases > 0.1.

Previous firmware don’t implement the register address 0x1n84 as well as the 0x1n70, the self-trigger is intended only

as the over/under threshold signal and a trigger request is intended only as the OR of the self-triggers couple.

Loading...

Loading...