T5L_ASIC Development Guide

D

WI

N

T

echnology

Pro

f

essional

,

Credi

t

able

,

Success

f

ul

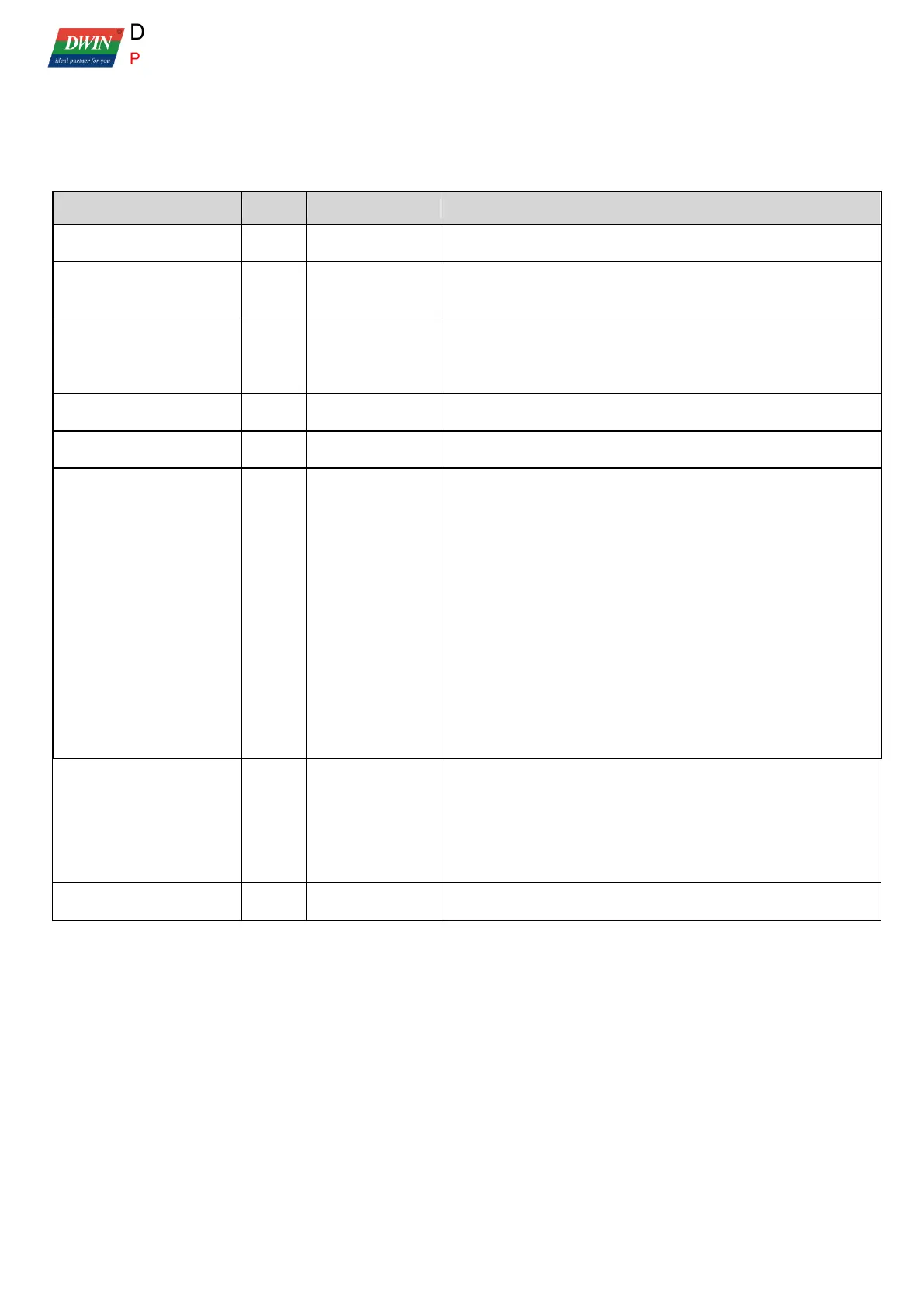

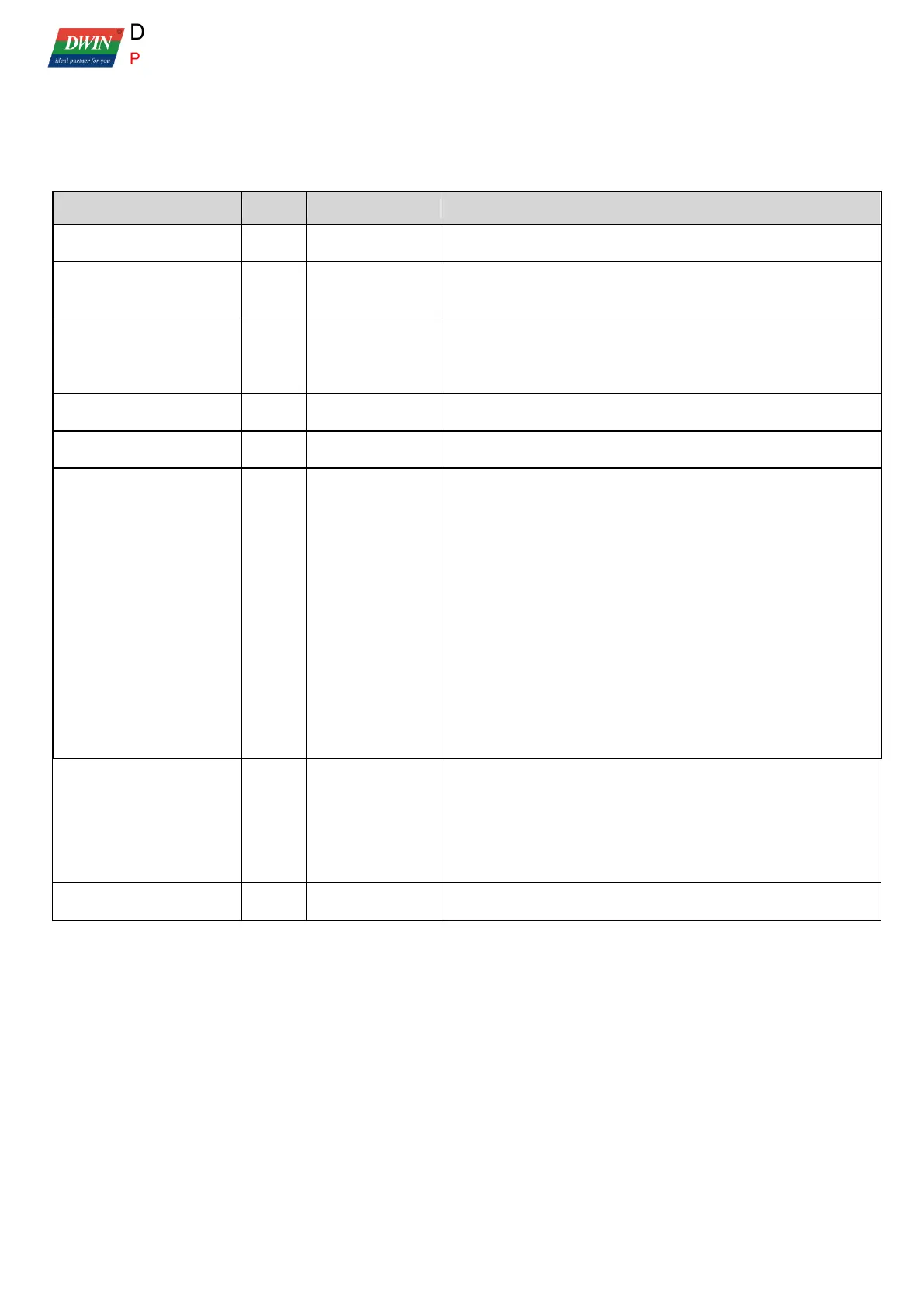

3.1 Initial Configuration

When the 8051 kernel is powered on, the special function register (SFR) in the following table must

be initialized correctly.

Configure extended interrupt system;

configure timer T2 to run in autoload mode

The change mode of DPTR after MOVX instruction operation must

be configured to 0x00 if developed with C51.

0x00: No change. 0x01: DPTR=DPTR+1. 0x03: DPTR=DPTR-1.

32KB RAM space accessed by MOVX: 0x8000-0xFFFF

0x60 or configuration

according to

application needs

Peripheral multiplexing selection:

.7 1 = CAN interface leads to P0.2, P0.3, 0 = CAN interface does

not lead out, and it works as an IO interface;

.6 1 = UART2 interface leads to P0.4, P0.5, 0 = UART2 interface

does not lead out, and it works as an IO interface;

.5 1 = UART3 interface leads to P 0.6, P 0.7, 0 = UART3 interface

does not lead out, and it works as an IO interface;

.4-.2 Reserved;

.1 WDT control 1=open 0=close;

.0 WDT feed dog, 1=feed the dog one time(The WDT count

becomes zero, and the watchdog's overflowing time is one

second. );

Driver capability configuration of IO port output mode.

0x00=4mA

0X01=8mA

0X02=16mA

0X03=32mA

DGUS variable memory access interface control

Loading...

Loading...