T5L_ASIC Development Guide

D

WI

N

T

echnology

Pro

f

essional

,

Credi

t

able

,

Success

f

ul

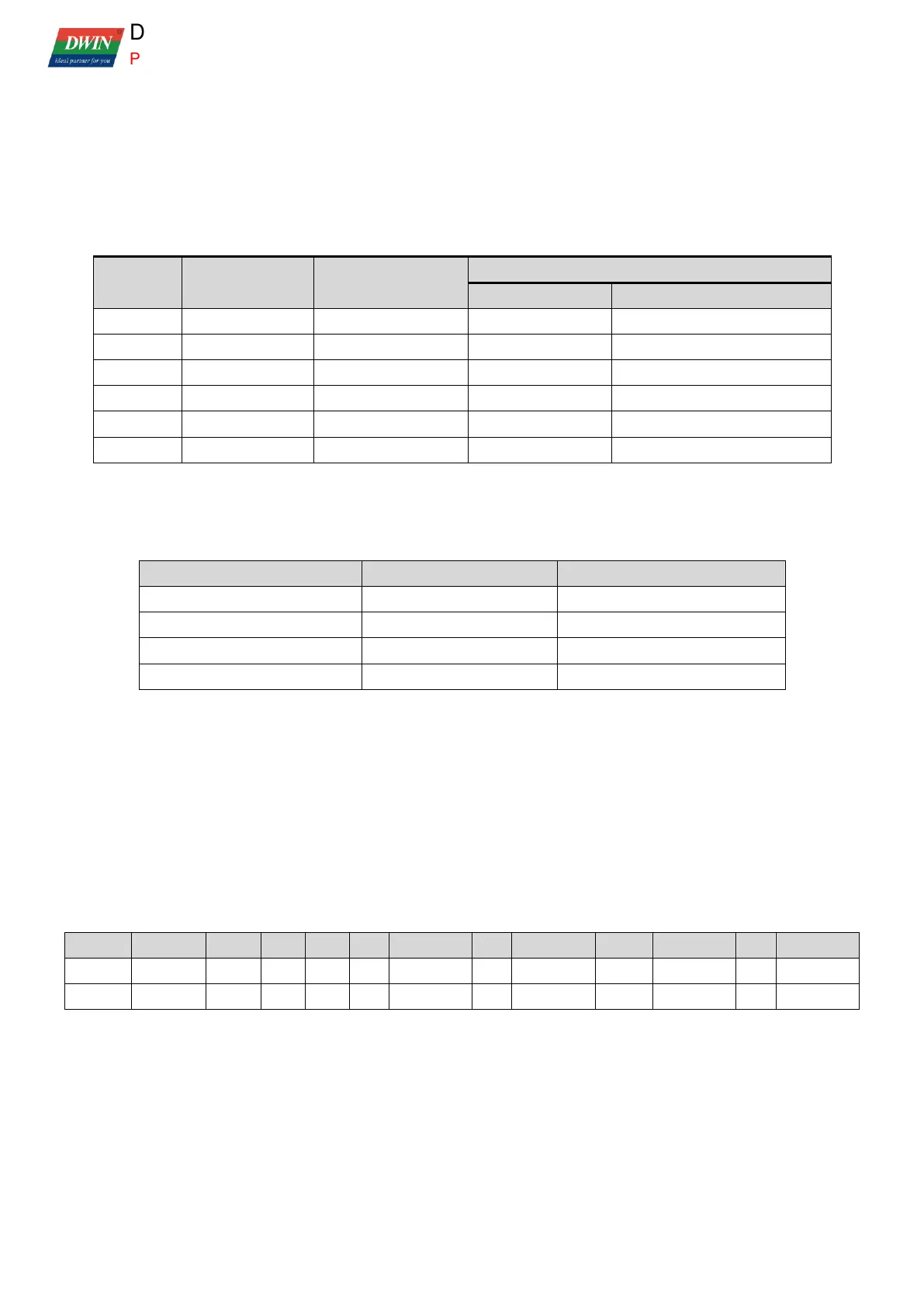

3.9.2 Interrupt Priority

The interrupt priority of T5L OS CPU is handled according to the following rules.

(1) Twelve interrupts are divided into six groups with two interrupts in each group. The priority in the

same group is fixed. For example, the priority of interrupt 0 is higher than that of UART3, as shown in

the table below.

CAN communication interrupt

(2) There are four levels of priority among the six groups, which can be configured by the

corresponding bits of IP0 and IP1 according to the table below.

For example, if you want to set the G2 group's T2 timer interrupt and UART5 receive interrupt priority

to the highest, you can set 1P1=0x20, 1P0=0x20.

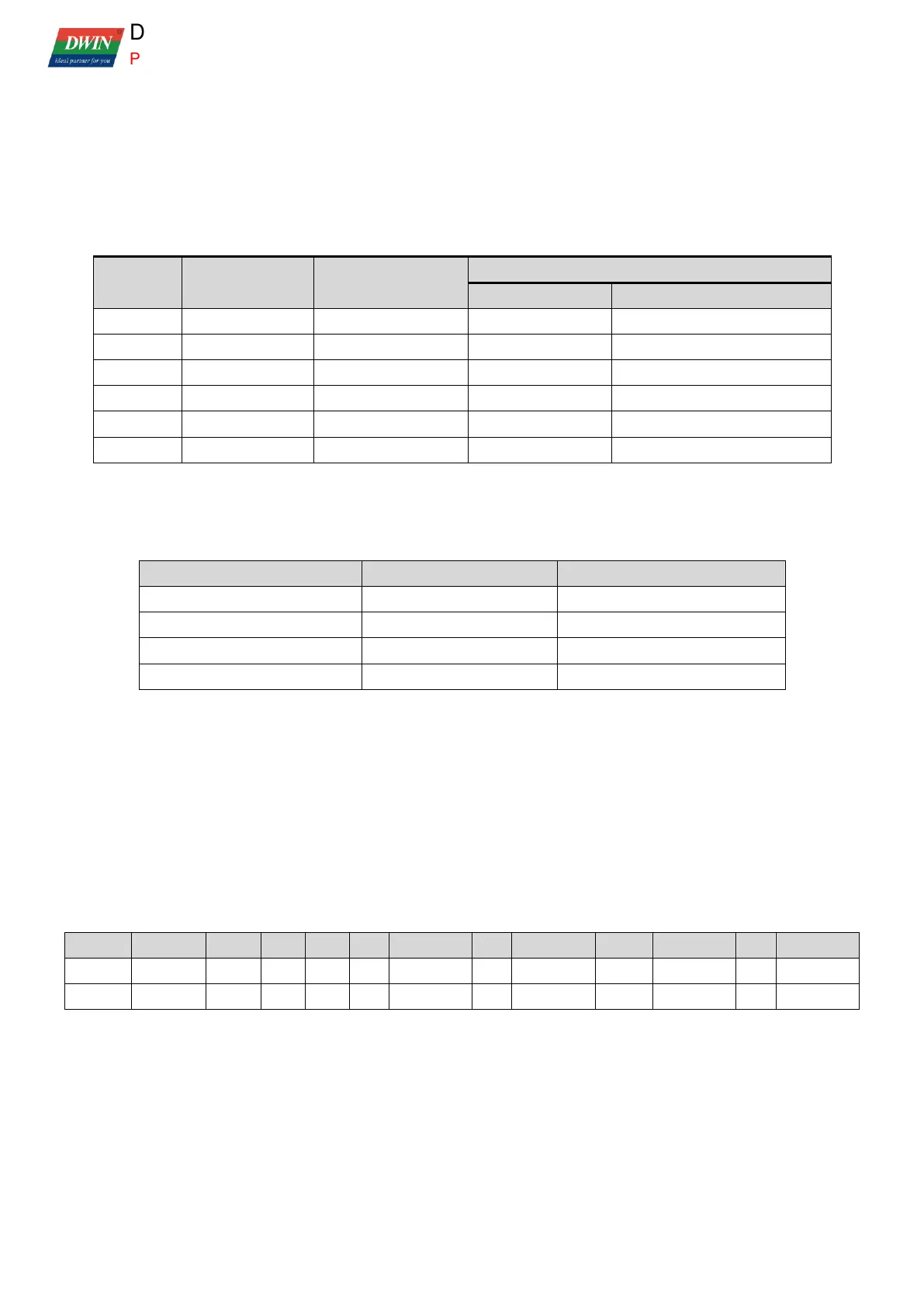

(3) If the configurations have the same priority (IP1 = 0x00 IP0 = 0x00), the G0 group has the highest

priority and the G5 group has the lowest priority. The interrupt priority weights with the same

configuration are as follows:

(4) High priority interrupts can be embedded in low priority interrupts (i.e. interrupts with small

weights can be interrupted by interrupts with large weights), and at most four levels can be

embedded.

Loading...

Loading...