Transmission Line Theory Applied to Digital Systems

Transmission Line Design

11-12

(8)

Solving equation 8, V

1

= 0.58 V. The implication of this result is that stubbing

off the line with gate loads in a distributed fashion is not recommended, due to

the reduced initial voltage swing. However, it would be acceptable to lump the

loads at the end of the line.

Since the value of the load resistor is greater than the characteristic impedance,

the voltage swing at the load resistor is greater than v1 by the amount of ρ

L

V

1

,

(in this example, 193 mV). When t = T

D

+ T

1

, the voltage at B is equal to 0.387

V; so 82 mV of undershoot occurs. Undershoot on the falling edge is defined as

the amount of voltage step above the nominal logic 0 level of 0.305 V. Overshoot

in the low logic state is defined as the amount of voltage change below the logic

0 level.

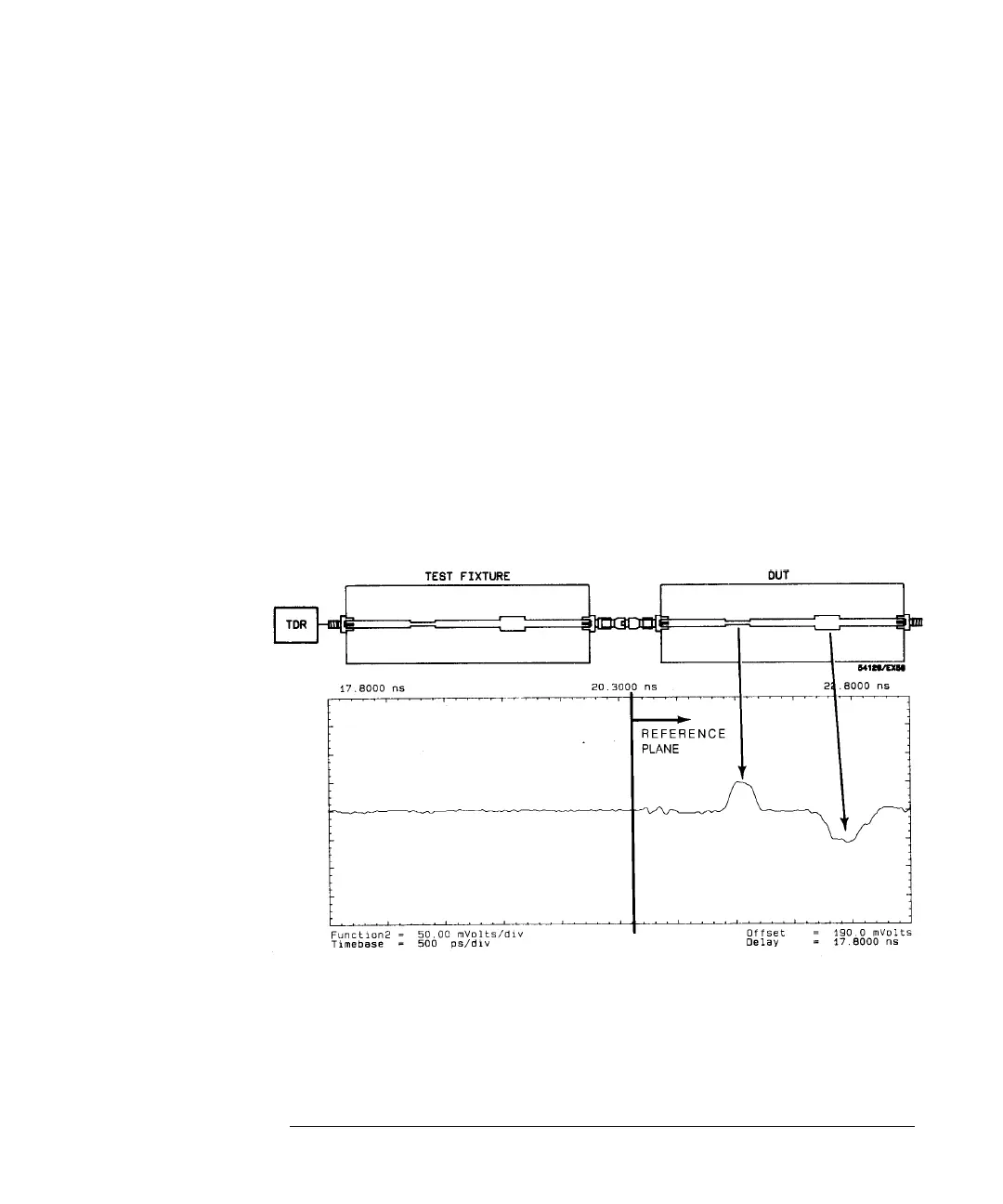

Figure 11-6

Voltage Waveforms for Points A and B in Example 2

In Figure 11-6, the voltage waveforms at points A and B of this example are

shown as a function of time. To be more realistic, the waveform in the figure is

shown to be a negative-going ramp rather than an abrupt step function. The

V

1

I

dc

–

()

Z

o

=

Loading...

Loading...