Message available bit (Output queue)

The summary bit of the output queue provides enabled summary information to Bit B4 (MAV) of the

status byte.

The Message Available Bit (MAV) is set when the Output queue holds data that pertains to the

normal operation of the instrument. The Output queue is one of the two System Switch/Multimeter

queues associated with the status model. The other queue sets the Error Available Bit (Error or Event

queue) (on page C-8). Both queues are first-in, first-out (FIFO) queues. The Status Byte Register

overview (on page C-3) shows how these queues are structured with regard to the other registers.

As an example, when a print command is sent, the response message is placed in the Output queue.

When data is placed in the Output queue, the Message Available (MAV) bit in the Status Byte

Register sets. A response message is cleared from the Output queue when it is read. The Output

queue is considered cleared when it is empty. An empty Output queue clears the MAV bit in the

Status Byte Register.

A message is read from the Output queue by addressing the System Switch/Multimeter to talk.

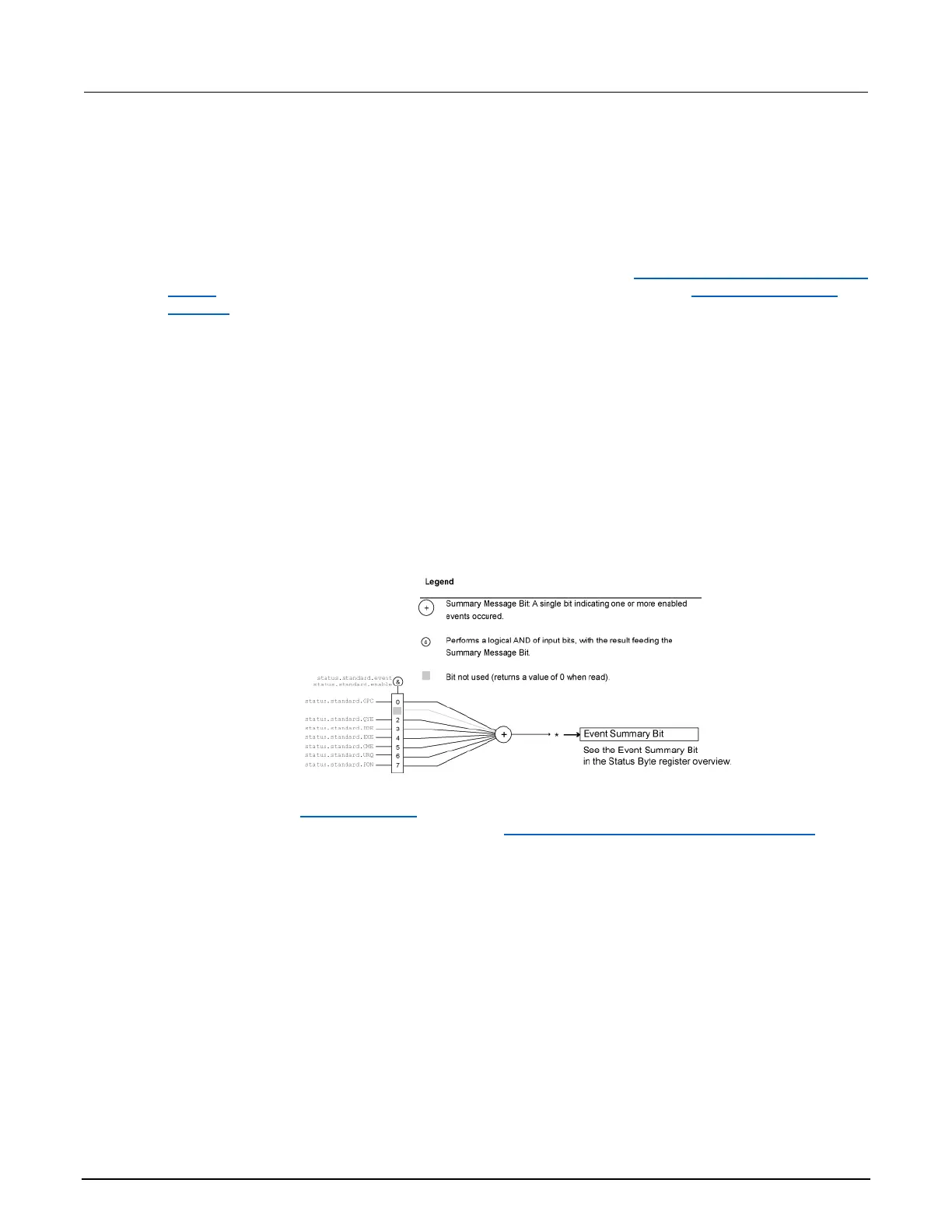

Event summary bit (ESB register)

The summary bit of the Standard event register provides enabled summary information to Bit B5

(OSB) of the status byte.

Figure 184: Event summary bit (Standard Event Register)

As shown above, there is only one register set associated with the event status register. Attributes

are summarized in status.standard.* (on page 11-391). Keep in mind that bits can also be set by

using numeric parameter values. For details, see Programming enable and transition registers (on

page C-14).

Loading...

Loading...