MIPI DSI to OpenLDI/FPD-Link/LVDS Interface Bridge Soft IP

User Guide

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are

trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02003-1.2 21

4.5. Running Functional Simulation

The generated IP package includes the behavioral models (<instance_name>_*_beh.v) provided in

\<project_dir>\dsi2fpdlink_eval\<instance_name>\src\beh_rtl for functional simulation. PLL wrapper

(pll_wrapper.v) in \<project_dir>\dsi2fpdlink_eval\models\lifmd and parameters file

(<instance_name>_params.v) in \<project_dir> are also needed for functional simulation. The testbench files

are provided in \<project_dir>\dsi2fpdlink_eval\testbench.

To run the evaluation simulation on Active-HDL (Windows only) follow these steps:

1. Create new project using Lattice Diamond for Windows.

2. Open Active-HDL Lattice Edition GUI tool.

3. Modify the *.do file located in \<project_dir>\dsi2fpdlink_eval\<instance_name>\sim\aldec\

a. Specify working directory, for example

set sim_working_folder "C:/my_design"

b. Specify workspace name that will be created in working directory, for example

set workspace_name "design_space"

c. Specify design name, for example

set design_name "DesignA"

d. Specify design path where the IP Core generated using Clarity Designer is located, for example

set design_path "C:/my_designs/DesignA"

e. Specify design instance name (same as the instance name specified in Clarity Designer), for example

set design_inst "DesignA_inst"

f. Specify Lattice Diamond primitive path to where it is installed, for example

set diamond_dir "C:/lscc/diamond/3.8_x64"

4. Update testbench parameters and/or directives to customize data size, clock and/or other settings. See Table 4.2

for the list of valid testbench compiler directives.

5. Click Tools, then click Execute macro.

6. Select the *.do file.

7. Wait for the simulation to finish.

Testbench parameters and directives can be modified by setting the define in the vlog command in the *.do file.

Table 4.2 is a list of testbench directives.

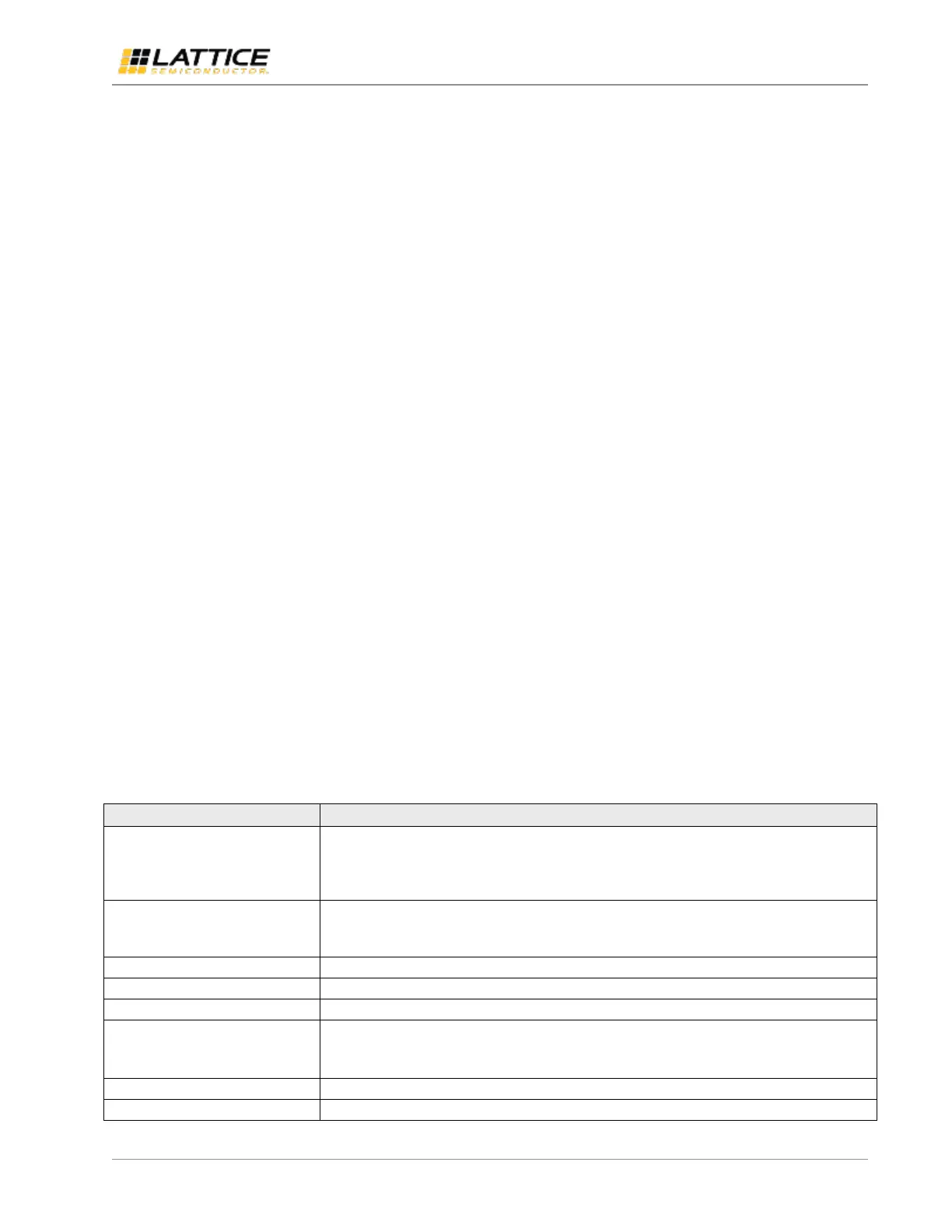

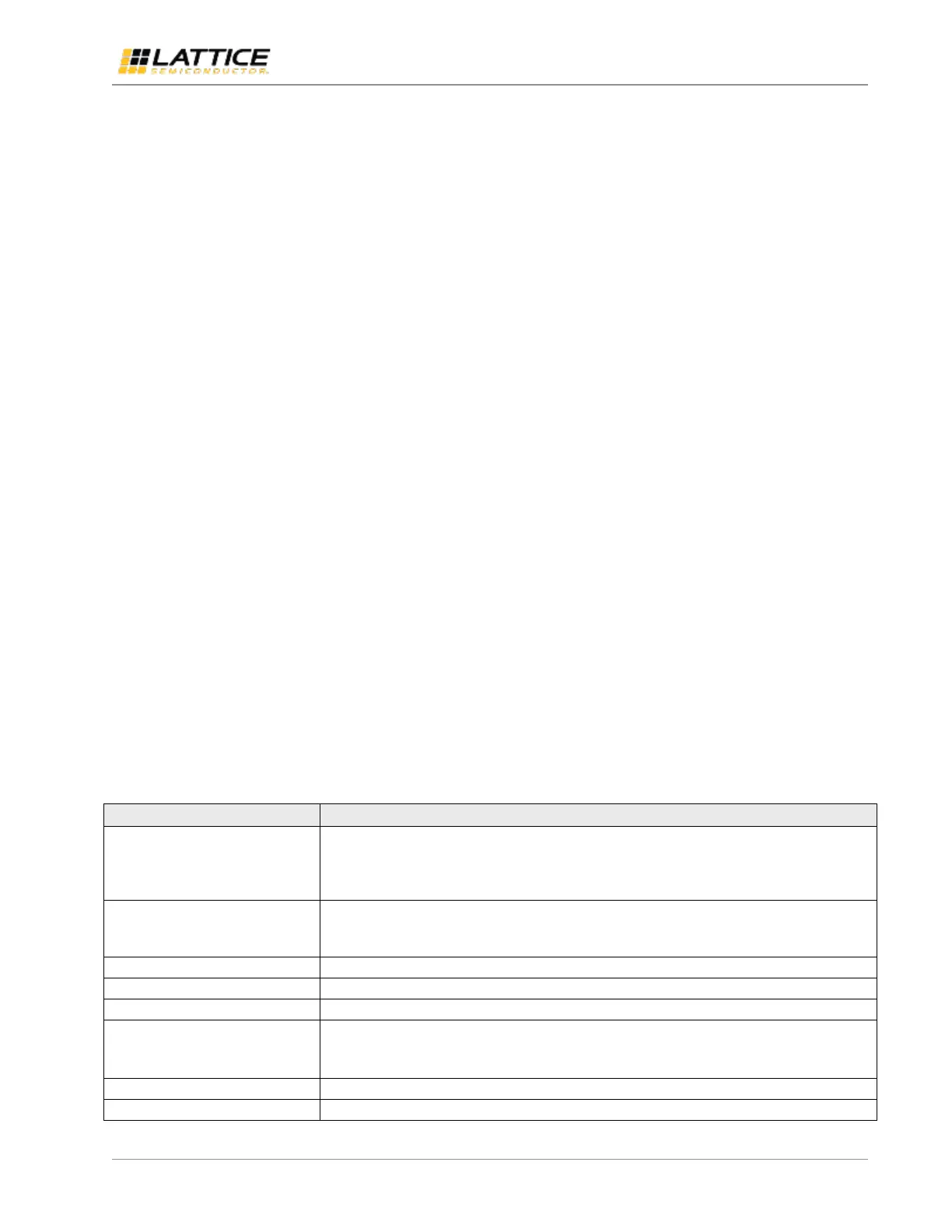

Table 4.2. Testbench Directives

Used when miscellaneous signals are off. For example, debug output port for ready_o and PLL

lock are not included in the generated design. This directive is used to set the duration (in ps)

of ready_o assertion before the DSI model in the testbench transmits input data to the design.

Example: +define+READY_DURATION=2000000

Used to drive low-power blanking. The user needs to define this in vlog. If this is not defined,

the testbench drives HS data as blanking.

Example: +define+LP_BLANKING

Used to set the number of video frames

Used to set the number of lines per frame

Used to set the virtual channel number

Used to enable or disable debug messages

0 – Debug messages disabled

1 – Debug messages enabled

Used to set the D-PHY clock period (in ps)

Used to set the low power mode delay between frames (in ps)

Loading...

Loading...