MIPI DSI to OpenLDI/FPD-Link/LVDS Interface Bridge Soft IP

User Guide

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are

trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

4 FPGA-IPUG-02003-1.2

1. Introduction

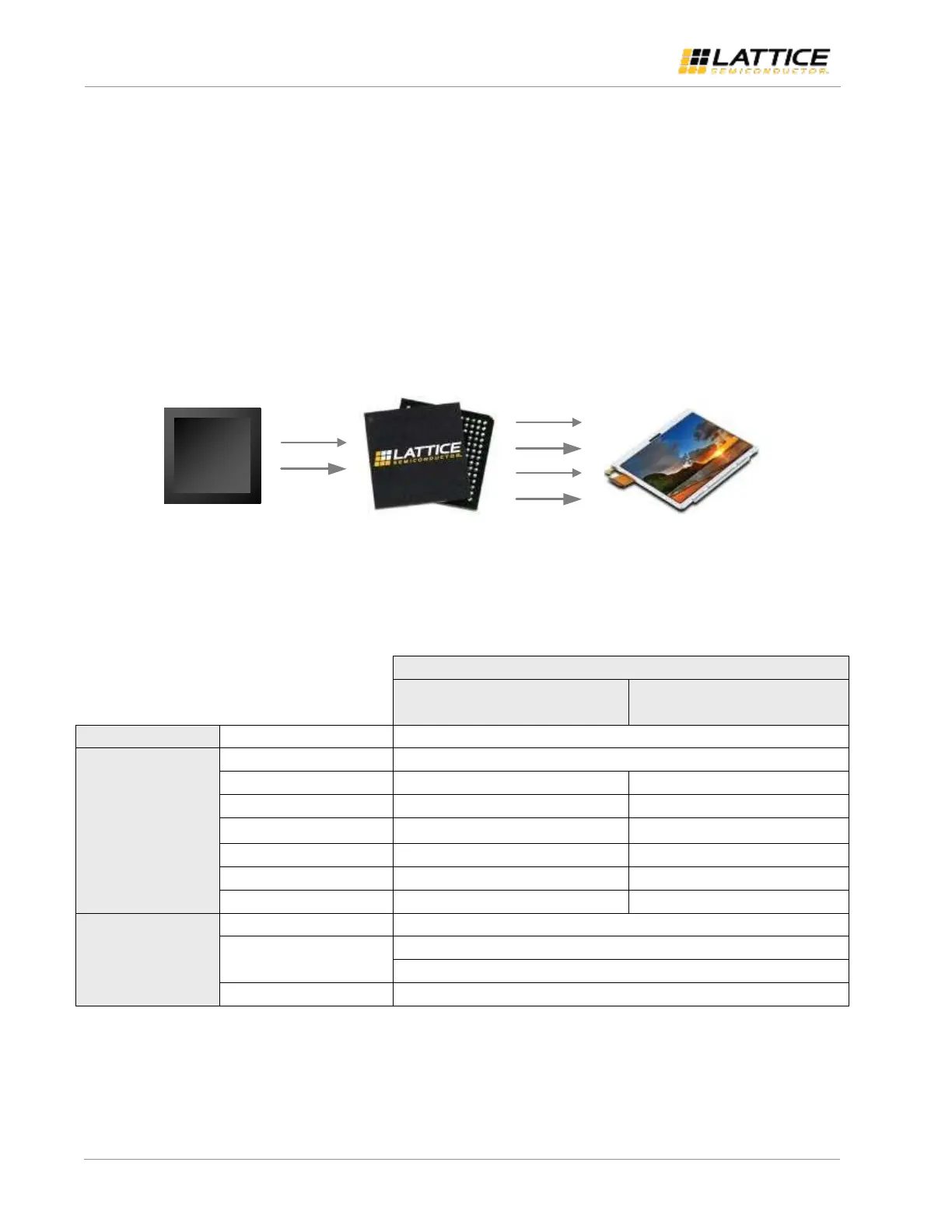

The Lattice Semiconductor MIPI

®

DSI to OpenLDI/FPD-Link/LVDS Interface Bridge IP with the Lattice Semiconductor

CrossLink™ programmable device can translate DSI video streams from MIPI D-PHY interface to LVDS interface for an

FDP-Link connection to displays.

The Mobile Industry Processor Interface (MIPI) provides specifications for standardization in consumer mobile devices.

MIPI Display Serial Interface (DSI) and MIPI D-PHY specifications were developed to create a standardized interface for

all displays used in the mobile industry. As the industry evolves, bandwidth requirements have exceeded what display

manufacturers are capable of manufacturing, while application processor vendors can provide very fast interfacing

capabilities. For a cost effective solution, displays can be replaced with newer display, and the processor can be

retained. Low Voltage Differential Signaling (LVDS) interface has become popular to support fast data rates of video

transmission for Flat Panel Display Link (FPD-Link) connections.

Application

Processor

DCK

MIPI DSI

LVDS

DCK0

D[0:3]

D0-D3

DCK1

D[4:7]

Figure 1.1. MIPI DSI to OpenLDI/FPD-Link/LVDS Interface Bridge System Diagram

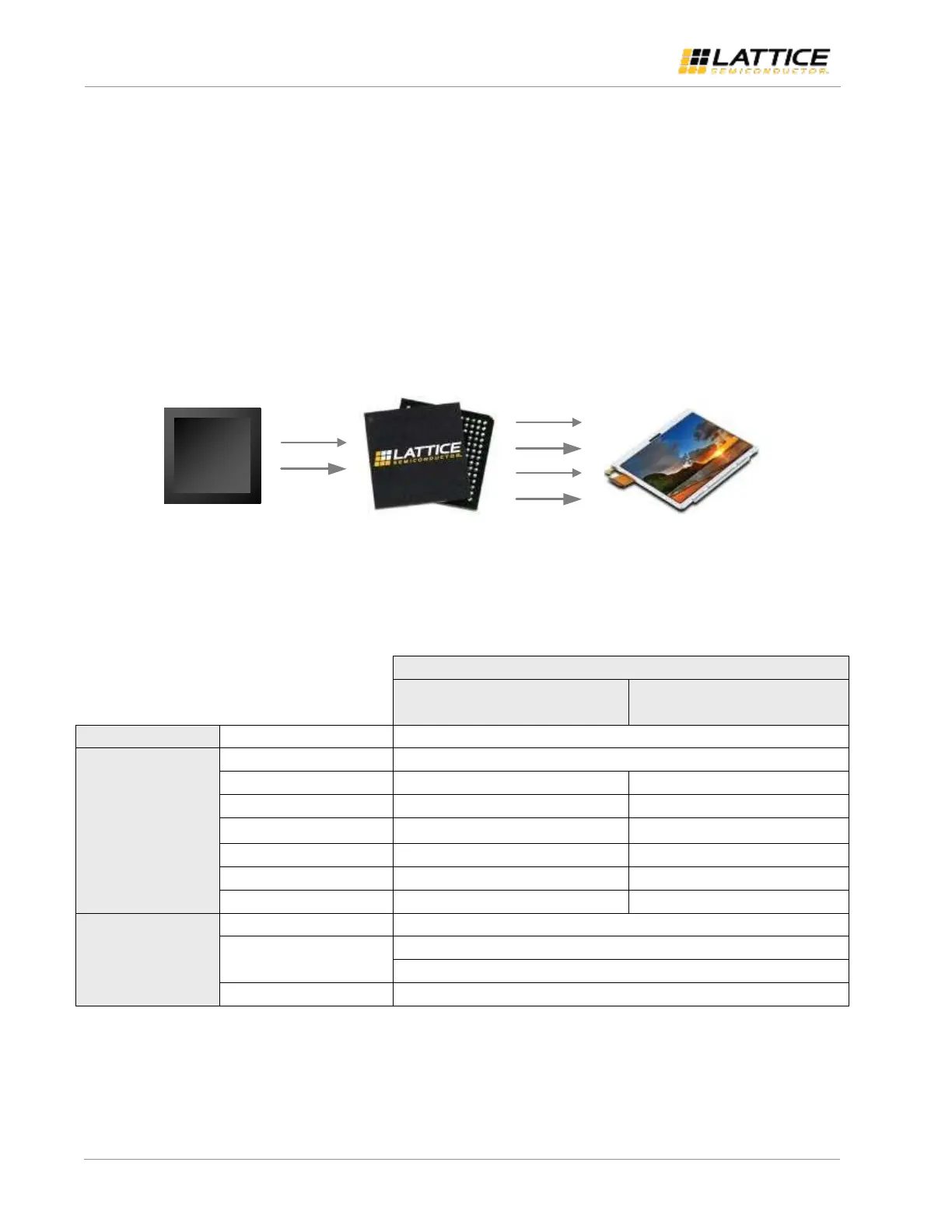

1.1. Quick Facts

Table 1.1 provides quick facts about the MIPI DSI to OpenLDI/FPD-Link/LVDS Interface Bridge IP for CrossLink device.

Table 1.1. MIPI DSI to OpenLDI/FPD-Link/LVDS Interface Bridge IP Quick Facts

MIPI DSI to OpenLDI/FPD-Link/LVDS Interface Bridge IP Configuration

Single MIPI DSI to Single FPD-Link

(RX_GEAR=8, RGB888, HS_LP)

Dual MIPI DSI to Dual FPD-Link

(RX_GEAR=16, RGB888, HS_LP)

32 bits total for 4 lanes

64 bits total for 4 lanes

Synopsys

®

Synplify Pro

®

L-2016.03L

Aldec

®

Active-HDL™ 10.3 Lattice Edition

Loading...

Loading...