12

TROUBLESHOOTING

12.7 Special Relay List

12 - 283

9

EMC AND LOW

VOLTAGE

DIRECTIVES

10

LOADING AND

INSTALLATION

11

MAINTENANCE AND

INSPECTION

12

TROUBLESHOOTING APPENDICES INDEX

*7: The Universal model QCPU except the Q02UCPU.

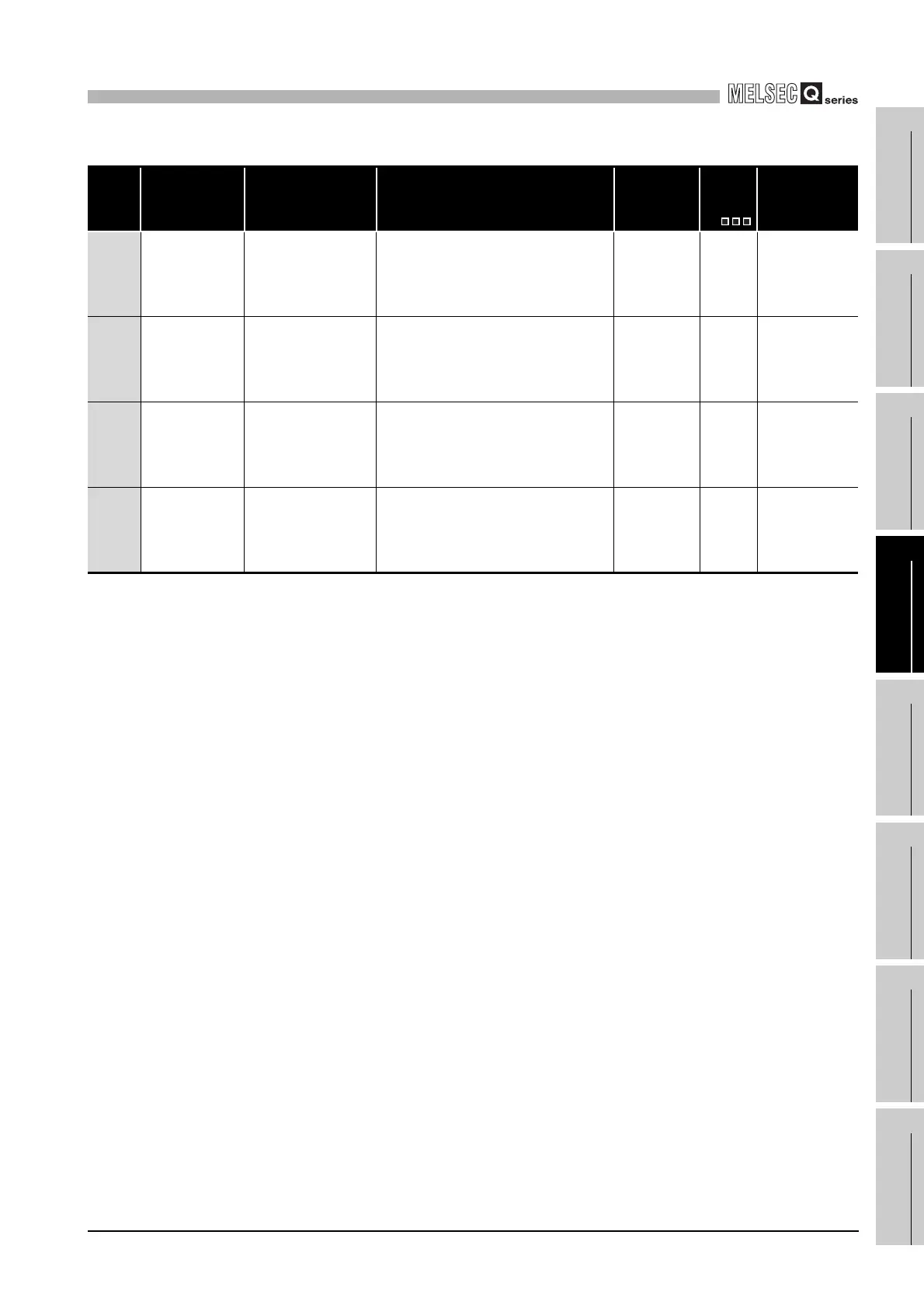

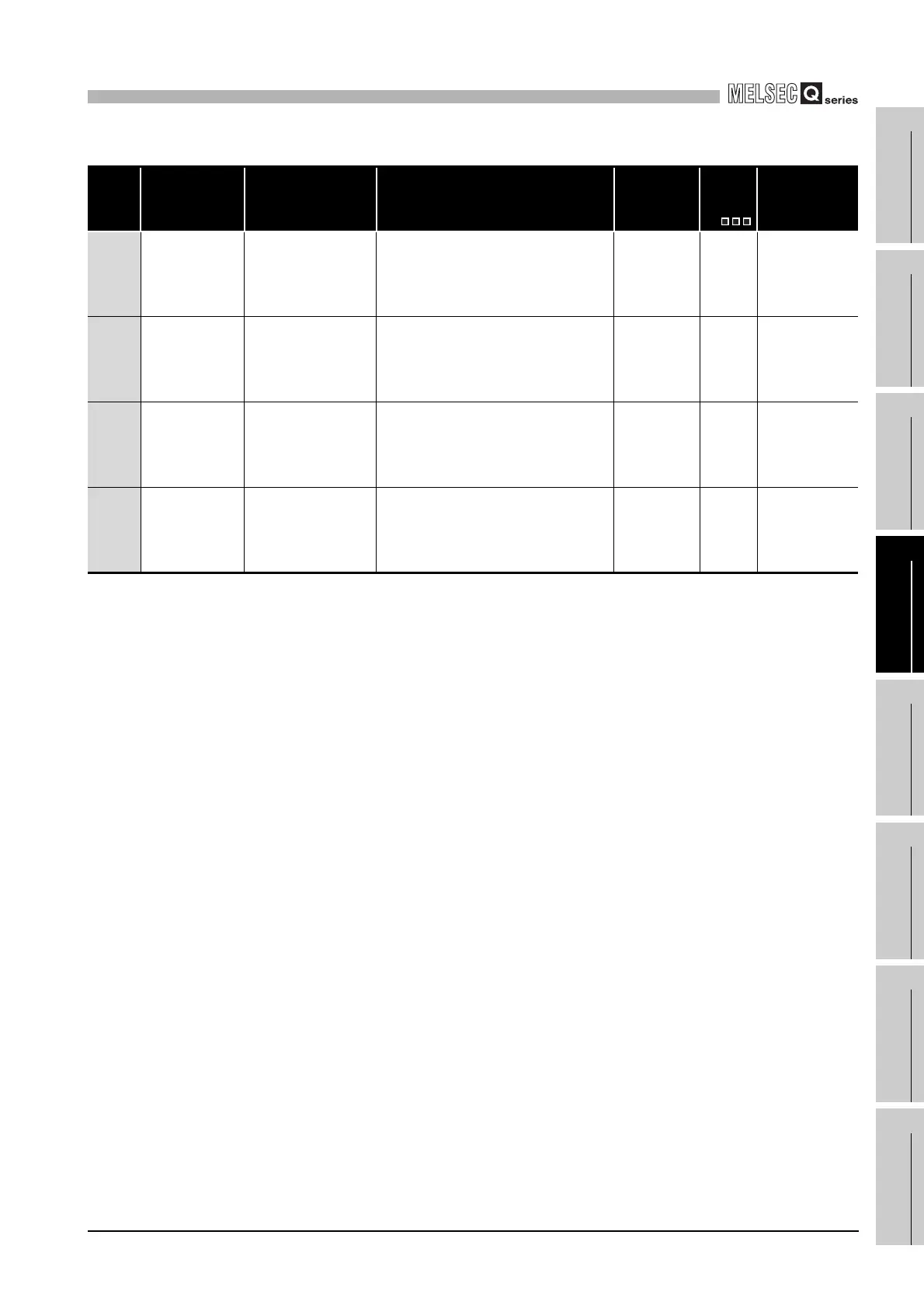

Table12.34 Special relay

Number Name Meaning Explanation

Set by

(When Set)

Corres-

ponding

ACPU

M9

Corresponding

CPU

SM796

Block information

using the multiple CPU

high-speed

transmission

dedicated instruction

(for CPU No.1)

OFF : Block is secured

ON : Block set by SD796

cannot be secured

• Turns ON when the number of the remaining blocks

of the dedicated instruction transmission area used

for the multiple CPU high-speed transmission

dedicated instruction (target CPU= CPU No.1) is less

than the number of blocks specified by SD796.

Turns ON at instruction execution. Turns OFF when

the empty area exists at END processing.

S (When

instruction/END

processing

executed)

New

QnU

*7

SM797

Block information

using the multiple CPU

high-speed

transmission

dedicated instruction

(for CPU No.2)

OFF : Block is secured

ON : Block set by SD797

cannot be secured

• Turns ON when the number of the remaining blocks

of the dedicated instruction transmission area used

for the multiple CPU high-speed transmission

dedicated instruction (target CPU= CPU No.2) is less

than the number of blocks specified by SD797.

Turns ON at instruction execution. Turns OFF when

the empty area exists at END processing.

S (When

instruction/END

processing

executed)

New

QnU

*7

SM798

Block information

using the multiple CPU

high-speed

transmission

dedicated instruction

(for CPU No.3)

OFF : Block is secured

ON : Block set by SD798

cannot be secured

• Turns ON when the number of the remaining blocks

of the dedicated instruction transmission area used

for the multiple CPU high-speed transmission

dedicated instruction (target CPU= CPU No.3) is less

than the number of blocks specified by SD798.

Turns ON at instruction execution. Turns OFF when

the empty area exists at END processing.

S (When

instruction/END

processing

executed)

New

QnU

*7

SM799

Block information

using the multiple CPU

high-speed

transmission

dedicated instruction

(for CPU No.4)

OFF : Block is secured

ON : Block set by SD799

cannot be secured

• Turns ON when the number of the remaining blocks

of the dedicated instruction transmission area used

for the multiple CPU high-speed transmission

dedicated instruction (target CPU= CPU No.4) is less

than the number of blocks specified by SD799.

Turns ON at instruction execution. Turns OFF when

the empty area exists at END processing.

S (When

instruction/END

processing

executed)

New

QnU

*7

Loading...

Loading...