SST-DN4-PCU Hardware Reference Guide

36 Hardware Register Details

©2009 Molex Inc.Automation & Electrical Products, Integrated Products Division

Document Edition: 1.0, Document #: 715-0101, Template Edition: 1.1, Template #: QMS-06-045

Use, duplication or disclosure of this document or any of the information contained herein is subject to the restrictions on page ii of this document.

3.4.6 HostIrq Register

The Irq function is supported in the PCI interface so the Irq support in this register is reserved.

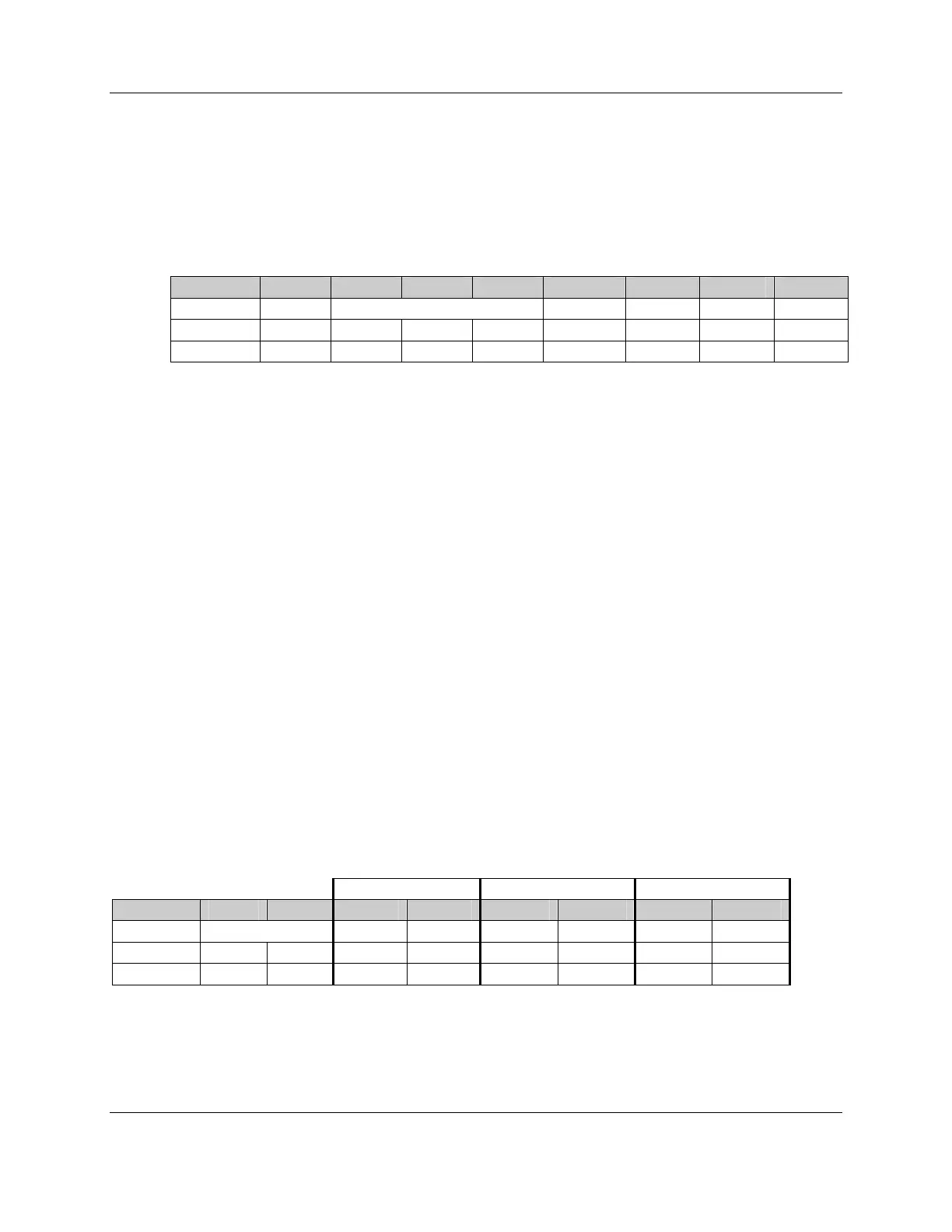

Table 15: HostIrq Register Settings

Bit 7 6 5 4 3 2 1 0

Name Platform Platform ID reserved reserved reserved reserved

Read/Write R/W R R R R R R R

Reset 0 0 0 0 0 0 0 0

The DN4 platform shall support DN3/DN4 hardware platform detection in the HostIrq register as

follows:

1) Writing 1000b in bits 7-4 shall cause bits 7-4 to subsequently read a platform. This code shall

only be non-zero for DN4 and above. The initial write of 1000b to bits 7-4 is to ensure old

drivers will not see a value in these bits that it is not expecting, DN, DNP and DN3 expect 0000b

and writing these bits did nothing.

2) DN4 platform shall read 0001b only if the previous access to the cards registers wrote “1” to

the Platform bit. When the Platform is set then the next access, read or write, will clear the

Platform bit.

3.4.7 LedReg Register

This register reflects the state of the channel’s LEDs, allowing host software to monitor the

LEDs and display them on-screen.

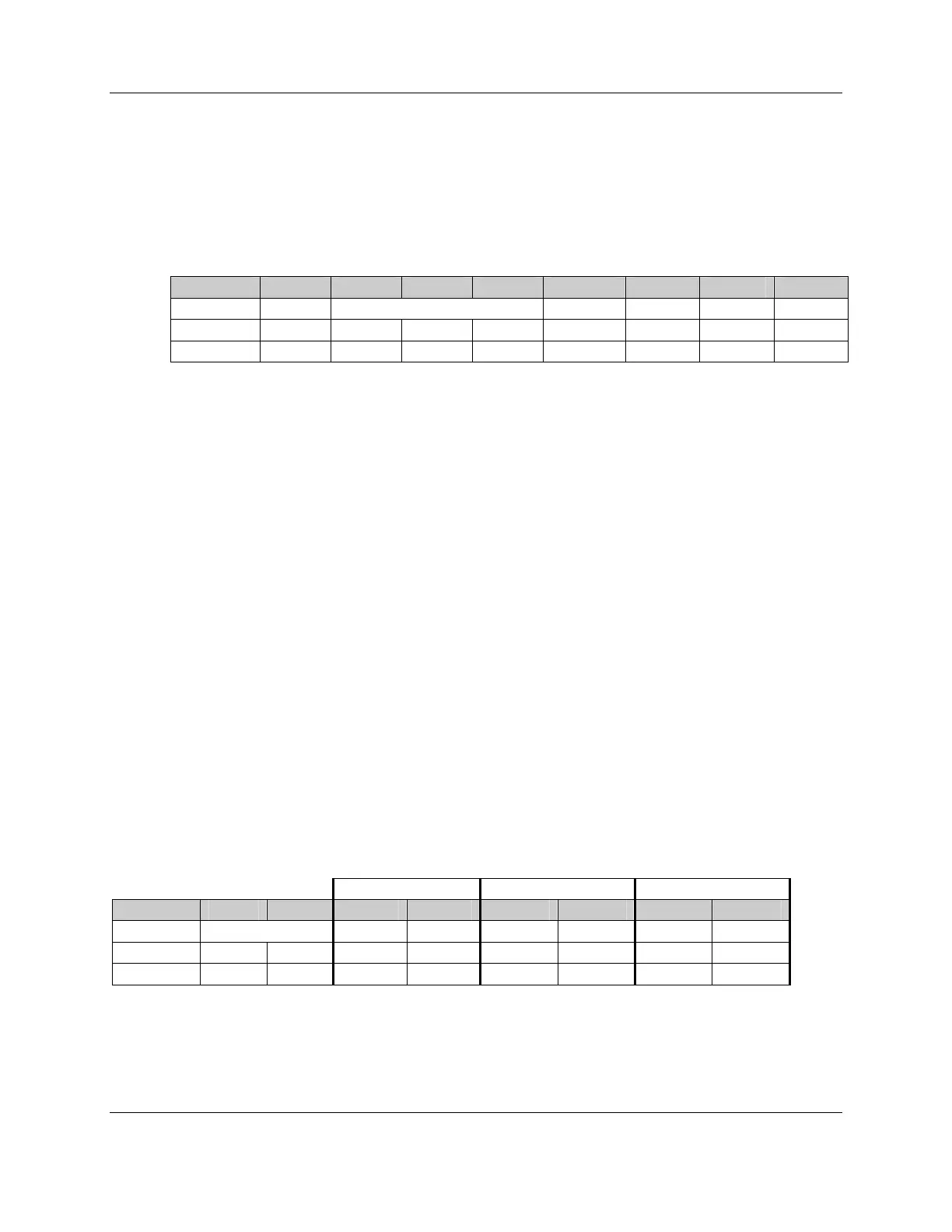

Table 16: LedReg Register Settings

PWR HLTH COMM

Bit 7 6 5 4 3 2 1 0

Name Reserved PwrRed PwrGrn HealthRed HealthGrn CommRed CommGrn

Read/Write R R R R R R R R

Reset 0 0 0 0 0 0 0 0

Loading...

Loading...