Platform Adaptation and Bring-Up

Jetson Nano Platform Adaptation and Bring-Up Guide DA_09361-002 | 10

The Jetson P3449 carrier board is designed and verified for one USB 3.0 port. The

verified use cases and their UPHY lane assignments are shown in Table 1 and Table 2.

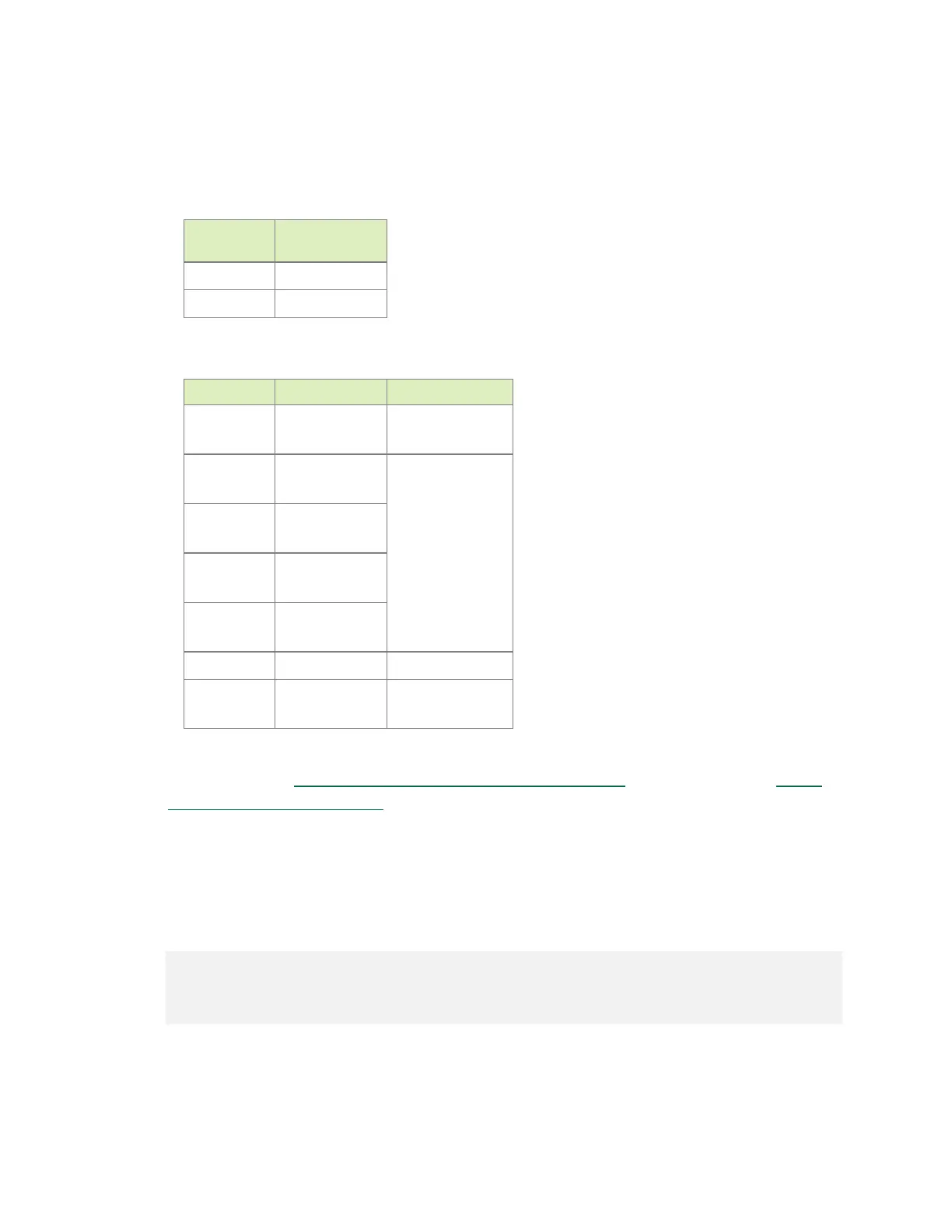

Table 1. Available outputs for the P3449 carrier board

Output

Type

Number of

Outputs

USB 3.0 1

PCIe 1 x4

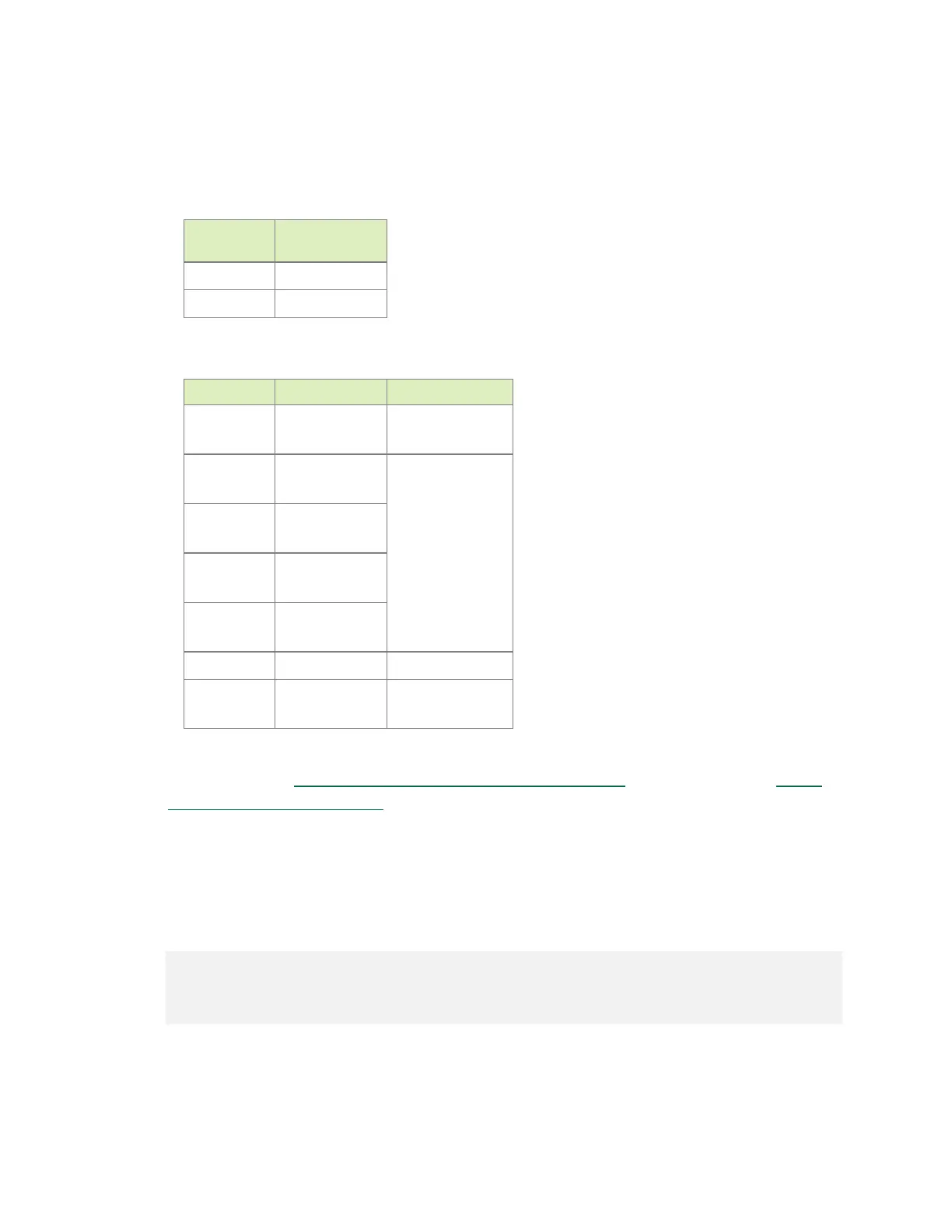

Table 2. UPHY lane assignment use cases

Lane Pin Names Functions

0 N/A

PCIe x1

C1

1

PEX_TX1

PEX_RX1

PCIe x4

C0

(L3/L2/L1/L0)

2

PEX_TX2

PEX_RX2

3

PEX_TX3

PEX_RX3

4

PEX_TX4

PEX_RX4

5 N/A N/A

6

PEX_TX6

PEX_RX6

USB3.0

P0

Jetson Nano and the supporting software are designed to support the configurations in

these tables. See Tegra X1 (SoC) Technical Reference Manual (TRM) and consult

Jetson

Nano Product Design Guide for further information before you design your custom

board. (Note that Tegra X1 Technical Reference Manual applies to Jetson Nano as well as

Jetson TX1.)

Lane assignment can be defined by the PCIe subnode under xusb_padctl in the

corresponding device tree file. The device tree’s xusb_padctl node follows the

conventions of the document:

kernel/kernel-4.9/Documentation/devicetree/bindings/pinctrl/pinctrl-

bindings.txt

The PCIe subnode lists the functions assigned to UPHY lanes.

• nvidia,function

Loading...

Loading...