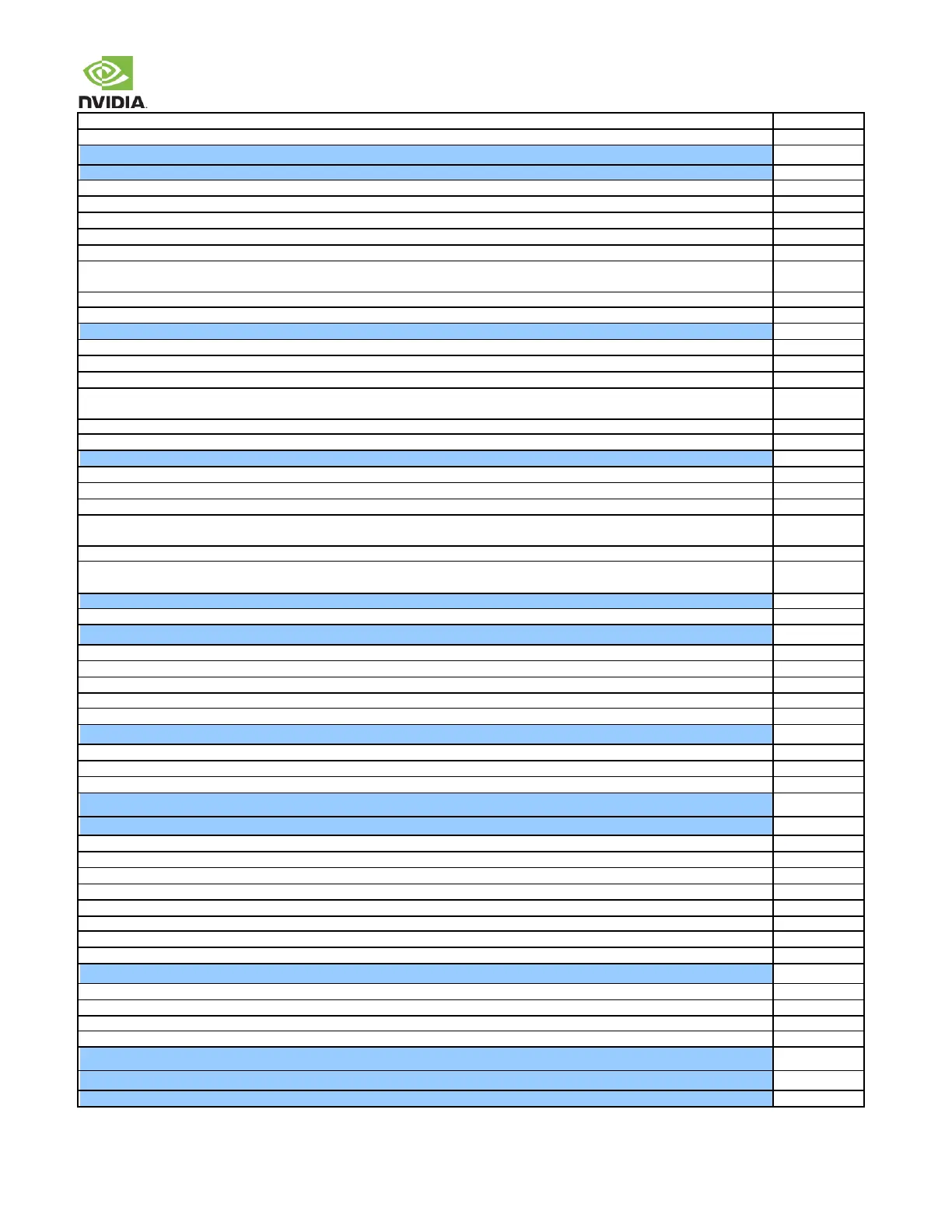

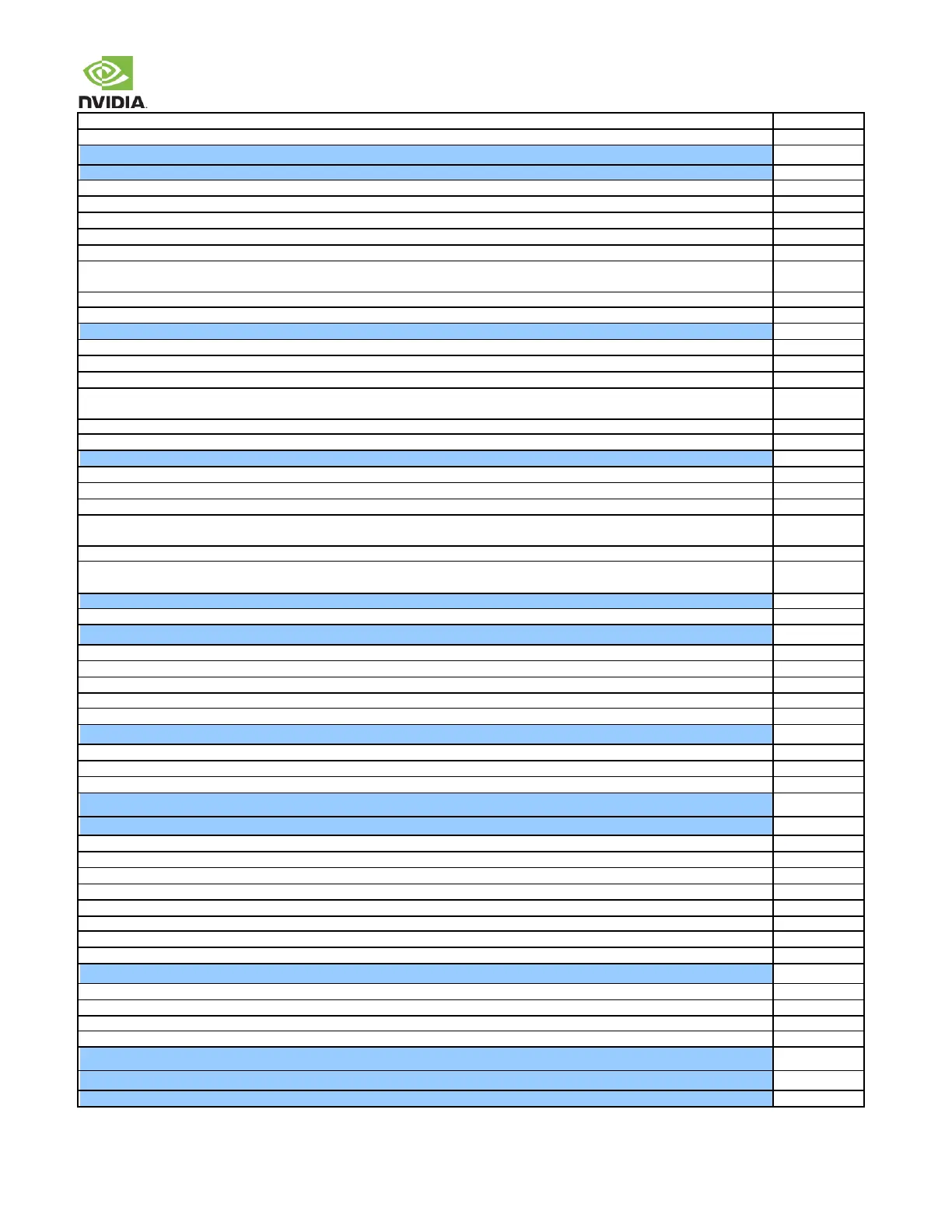

NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 82

See USB 3.0 section for Common Mode Choke requirements if this is required. TDK ACM2012D-900-2P device is recommended

See USB 3.0 section for ESD requirements. SEMTECH ESD Rclamp0524p device is recommended

PCIe Controller #0 (x1 by default – supports up to x4. Lanes [2:1] of x4 configuration shared w/USB_SS#[2:1]

PEX0 used for 3.3V single-lane device/connector (lane 0 of PCIe x1 connector on reference Carrier Board)

PEX0 & USB_SS1 used for 3.3V 2-lane device/connector

PEX0, USB_SS1, PEX2 & PEX_RFU used for 3.3V 4-lane device/connector

TX+/ connected to corresponding pins on connector, or RX+/ on device on the carrier board (See Signal Terminations)

RX+/ connected to corresponding pins on connector, or TX+/ on device on the carrier board

AC caps are provided for device TX pins (those connected to the module RX+/) if device is on the carrier board (See Signal

Terminations)

Reference clock used for PCIe Controller #0 (Up to x4 lane PCIe interface) is PEX0_REFCLK+/–

Clock Request & Reset for PCIe Controller #0 are PEX0_CLKREQ# & PEX0_RST#

PCIe Controller #1 (x1 – Shared with PCIe Controller #0 lane 2)

PEX2 used for 3.3V single-lane device/connector

TX+/ connected to corresponding pins on connector, or RX+/ on device on the carrier board (See Signal Terminations)

RX+/ connected to corresponding pins on connector, or TX+/ on device on the carrier board

AC caps are provided for device TX pins (those connected to the module RX+/) if device is on the carrier board (See Signal

Terminations)

Reference clock used for PCIe Controller #1 (single-lane PCIe interface) is PEX2_REFCLK+/

Clock Request & Reset for PCIe Controller #1 are PEX2_CLKREQ# & PEX2_RST# (See Signal Terminations)

PEX1 used for 3.3V single-lane device/connector (M.2 connector on Jetson carrier board) or USB_SS#0 (controlled by on module mux)

TX+/ connected to corresponding pins on connector, or RX+/ on device on the carrier board (See Signal Terminations)

RX+/ connected to corresponding pins on connector, or TX+/ on device on the carrier board

AC caps are provided for device TX pins (those connected to the module RX+/) if device is on the carrier board (See Signal

Terminations)

Reference clock used for PCIe Controller #2 (single-lane PCIe interface) is PEX1_REFCLK+/

Clock Request & Reset for PCIe Controller #1 are PEX1_CLKREQ# & PEX1_RST# (PEX1_CLKREQ# muxed with SATA_DEV_SLP on module -

See Signal Terminations)

PEX_WAKE# connected to WAKE pins on devices/connectors (See Signal Terminations)

SATA_TX+/– connected to TX_P/N pins of SATA connector (or RX+/ pins of onboard device) (See Signal Terminations)

SATA_RX+/– connected to RX_P/N pins of SATA connector (or TX+/ pins of onboard device) (See Signal Terminations)

See SATA section for Common Mode Choke requirements if they are required. TDK ACM2012D-900-2P device is recommended

See SATA section for ESD requirements. SEMTECH ESD Rclamp0524p device is recommended

SATA_DEV_SLP connected to matching pin on device or connector (pin 10 on conn. shown in SATA section See Signal Terminations)

GBE_MDI[3:0]+/ – connected to equivalent pins on magnetics device (See Signal Terminations)

GBE_LINK_ACT, GBE_LINK100 & GBE_LINK1000 connected to LED pins on connector (See Signal Terminations)

GBE_CTVREF Not used. Leave NC.

SDCARD_CLK connected to CLK pin of socket/device

SDCARD_CMD connected to CMD pin of socket/device. (See Signal Terminations)

SDCARD_D[3:0] connected to DATA[3:0] pins of socket/device. (See Signal Terminations)

SDCARD_CD connected to the SD Card Detect pin on socket

SDCARD_WP connected to the SD Card Write Protect pin on socket (if supported)

SDCARD_PWR_EN connected to SD Card VDD supply/load switch enable pin

Adequate bypass caps provided on SD Card VDD rail

Any EMI/ESD devices used are suitable for highest frequencies supported (low capacitive load: <1pf recommended).

SDIO_CLK connected to CLK pin of device

SDIO_CMD connected to CMD pin of device. (See Signal Terminations)

SDIO_D[3:0] connected to DATA[3:0] pins of device. (See Signal Terminations)

Any EMI/ESD devices used are suitable for highest frequencies supported (low capacitive load: <1pf recommended).

DSI Dual Link Configurations

Loading...

Loading...