Safety Manual for MPC5777M, Rev. 1.1

Functional safety requirements for application software

NXP Semiconductors46

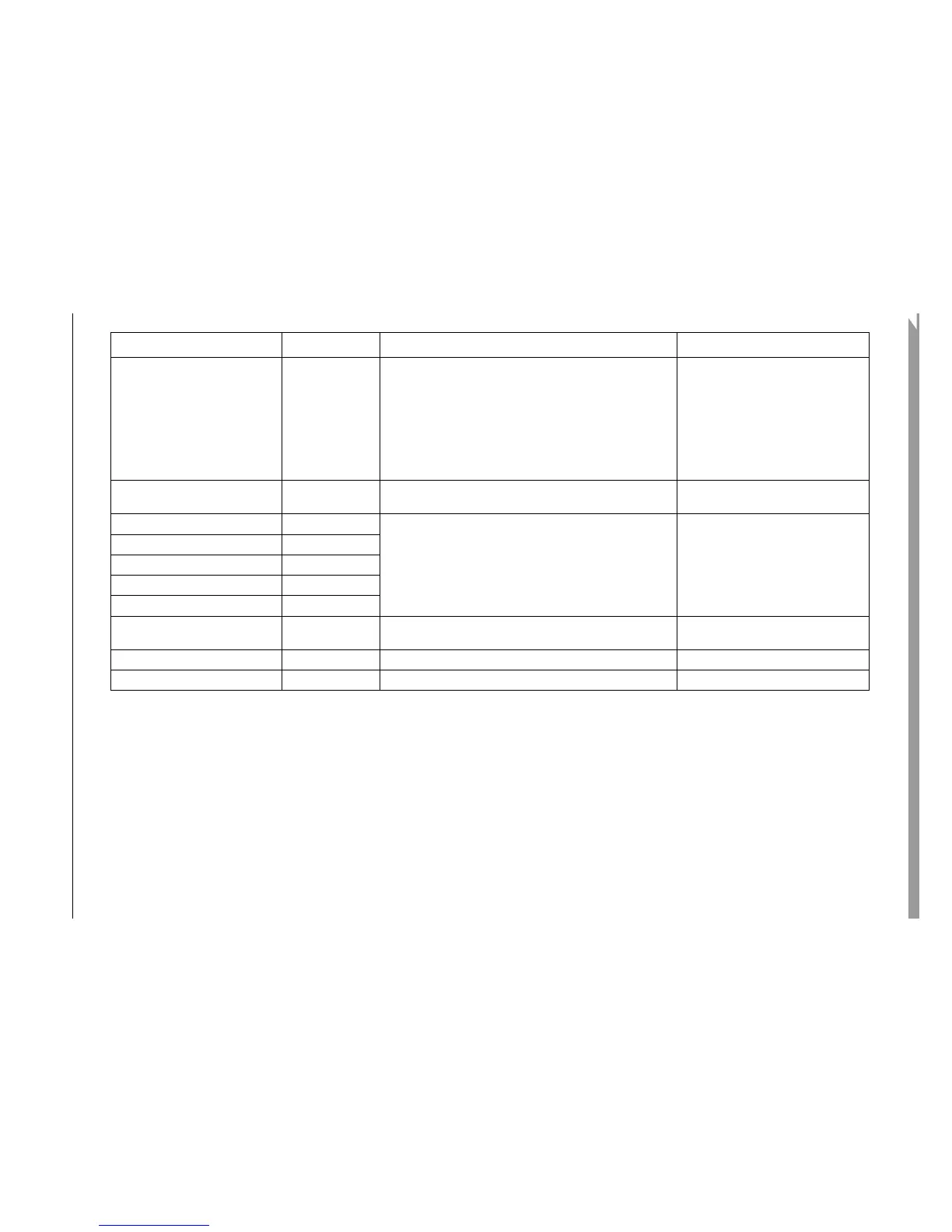

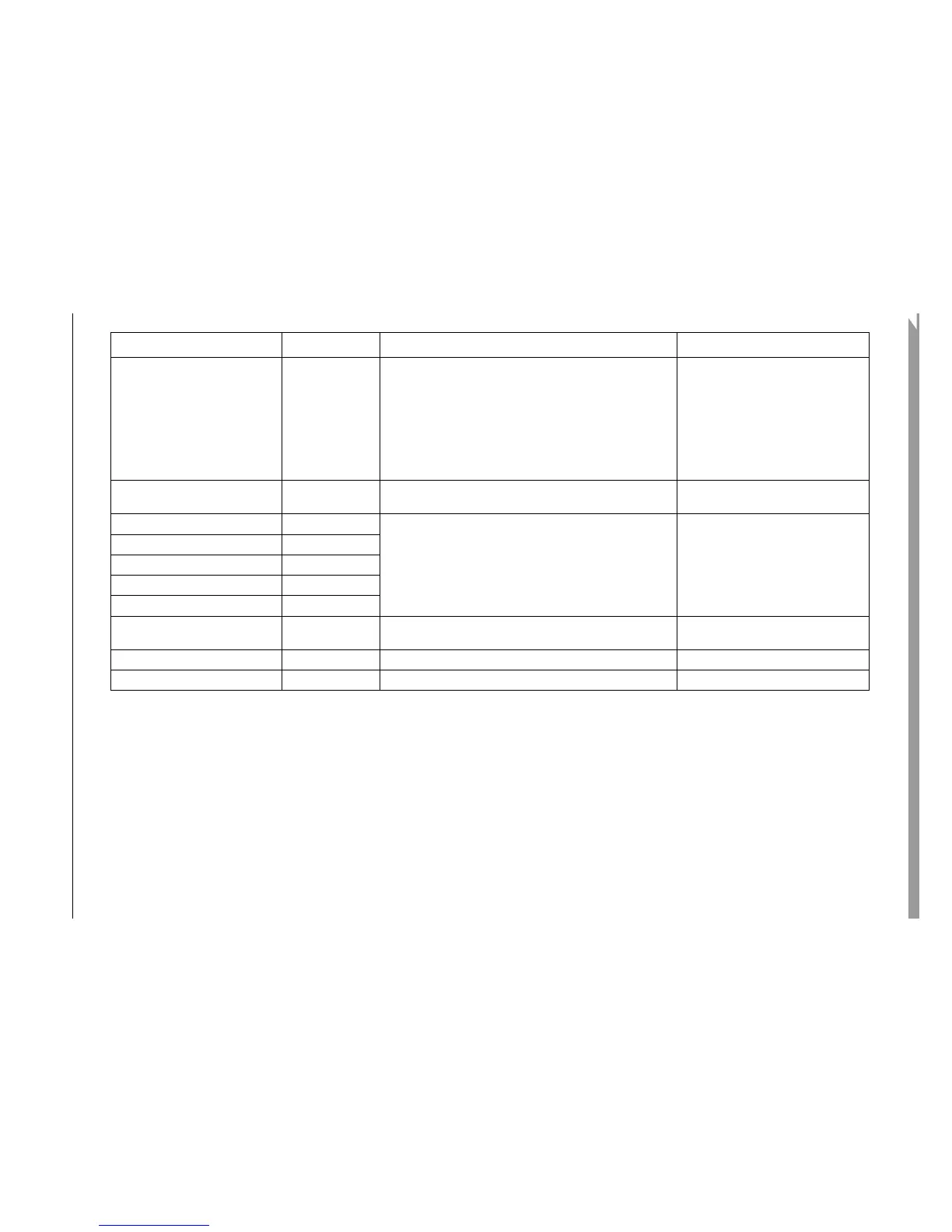

lfast_0 RGM_PRST[9] Module enable DRFENrst=0

After reset LFAST is immediately disabled. All current/pending

requests are terminated and the Tx and Rx data FIFOs are

flushed. If a reset occurs in the middle of a transmit/receive

operation, then that operation is terminated immediately and

nothing is transmitted/received further. Registers read/write

operations can be performed through the IPS Bus.

cansubsys (canram controller) RGM_PRST[74] CAN RAM CTRL is reset together with the CAN subsystem. NO, reset is detected via CAN

subsystem reset

cansubsys (can1) RGM_PRST[70] After reset bit 0 [INIT] of the CCCR register = `1' in the CC

Control Register and enables software initialization. The

M_CAN does not influence the CAN bus until the CPU resets

bit 0 [INIT] of the CCCR register = `0'

NO, after reset no communication is

performed on the bus

cansubsys (can2) RGM_PRST[69]

cansubsys (can3) RGM_PRST[68]

cansubsys (can4) RGM_PRST[67]

cansubsys (TTCAN) RGM_PRST[72]

EBI_0 RGM_PRST[3] NO, after reset all activity on EBI ports

are stopped

SIUL RGM_PRST[15] YES, application dependent

FCCU RGM_PRST[169] YES

Table 1. Effects of reset (continued)

Receiving module Software control Detection Software action required?

Loading...

Loading...