Safety Manual for MPC5777M, Rev. 1.1

Functional safety requirements for application software

NXP Semiconductors48

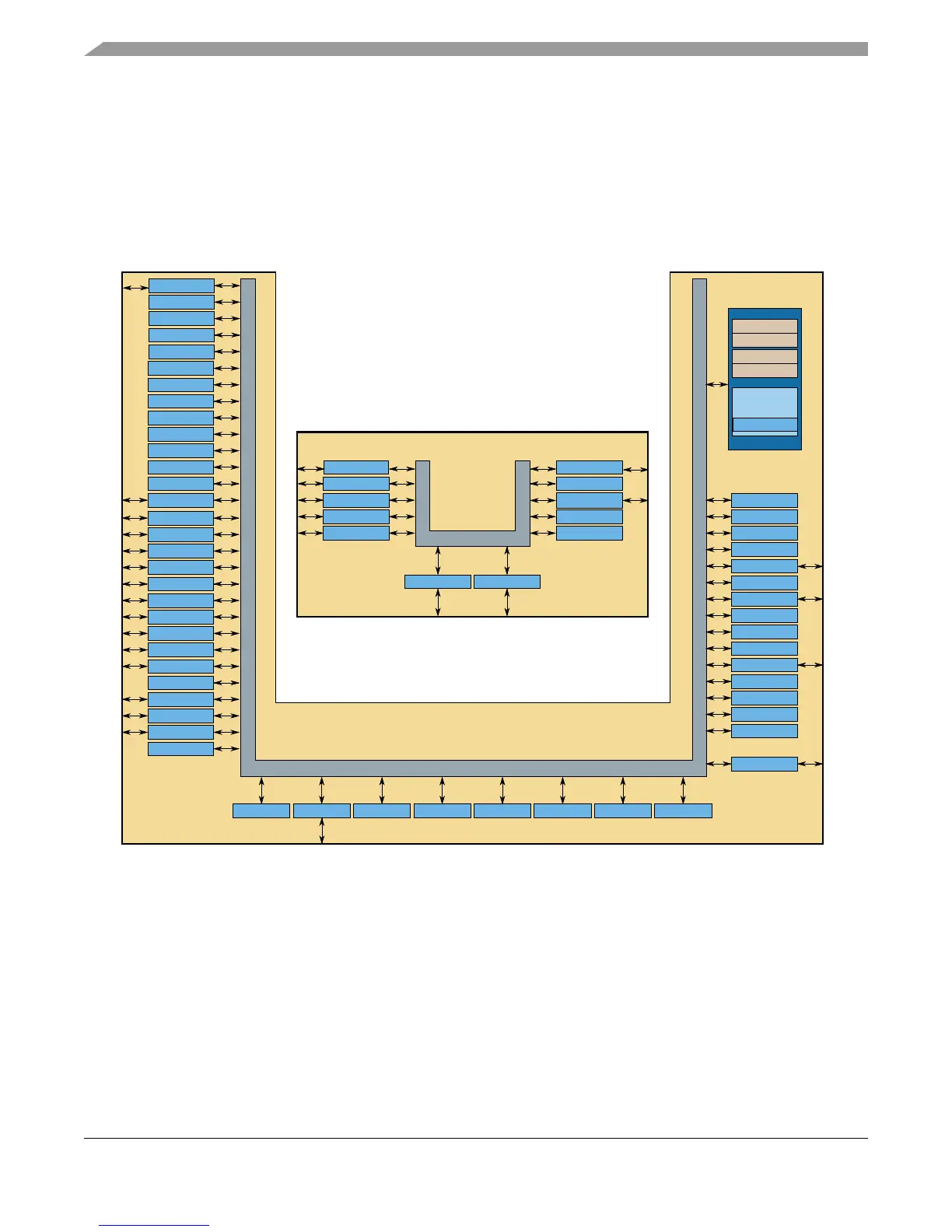

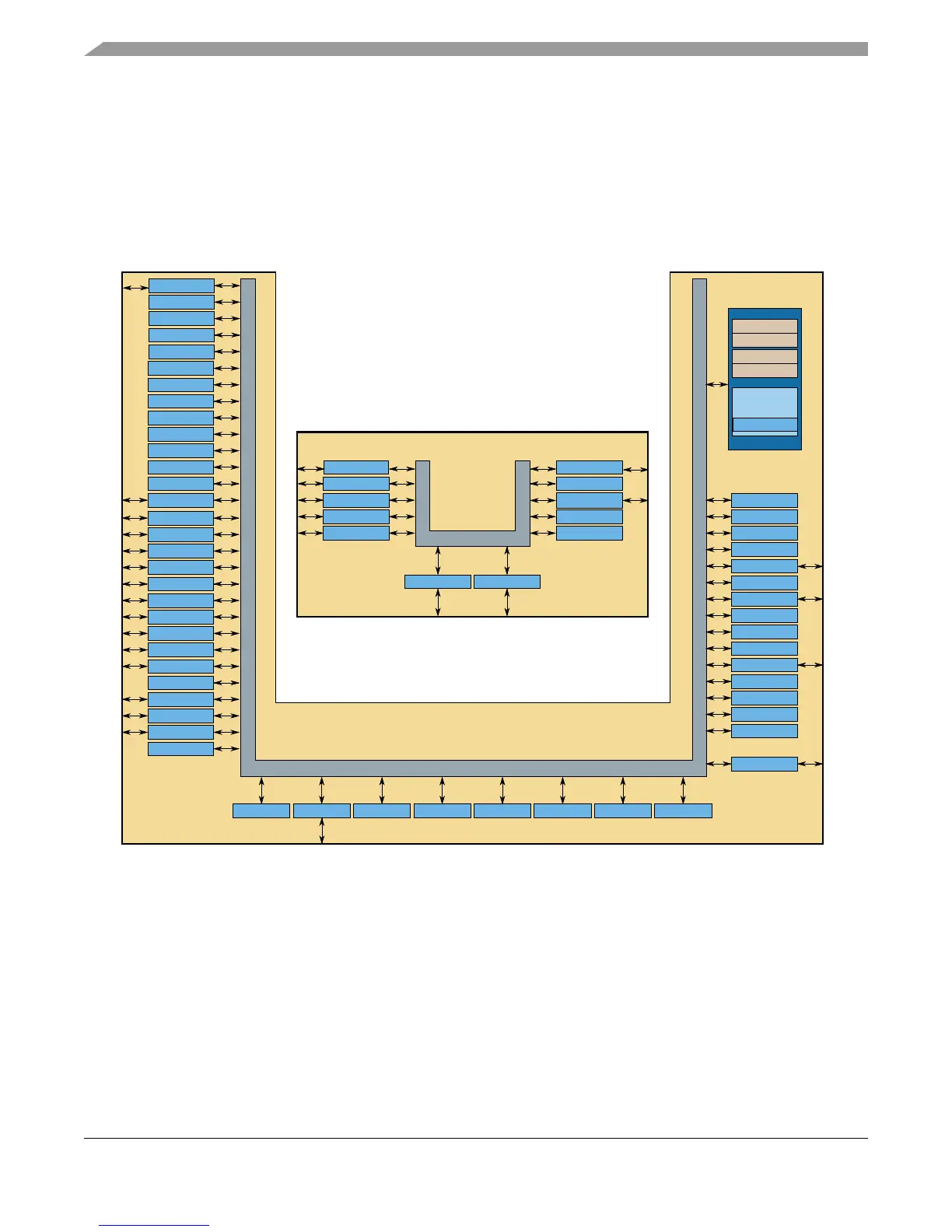

To allow a safety application to make redundant use of all I/O peripherals, the peripherals have two

instances and each instance is connected to a different peripheral bridge (PBRIDGE). The arrangement of

the I/O peripherals onto two PBRIDGEs allows redundant use of peripherals while limiting CCFs.

The MPC5777M architecture allows making redundant use of the communication peripherals like

LINFlexD, DSPI and PSI5. Figure 2 shows the distribution of the MPC5777M peripherals.

Figure 2. MPC5777M peripheral allocation

As a usage example, if an application needs to use LIN communications protocol, two different LINFlexD

modules may be used; one connected to the PBRIDGEA and one the PBRIDGEB.

Peripheral Bus (AIPS_0)

Peripheral

Cluster A

WKPU

LVIIO

LVIFLASH

LVI 1.2V

HVI 1.2V

PMC

PCU

RGM

CGM

RCOSC_DIG_0

OSC_DIG

CMU_PLL

ME

SUIL2

2 x SIPI

2 x LFAST

CFLASH_0

PASS

SSCM

BAF

PLL

PRAM

PFLASH

INTC_0

4 x SWT

3 x STM

2 x SMPU

3 x SAR ADC

PSI5_0

FLEXRAY_0

SENT_0

IIC_0

5 x DSPI

4 x LINFlexD

4 x MCAN

TTCAN_0

HSM INTERFACE

DTS

JDC

SRAM CAN

5 x SD ADC

2 x DMA

FEC

GTM

2 x LINFlexD

5 x SD ADC

9 x SAR ADC

PSI5_1

SENT_1

3 x DSPI

12 x CMU

CRC_1

FCCU

Peripheral Bus (AIPS_1)

Peripheral

Cluster B

JTAGM

STCU2

MEMU

IMA CRC_0

10 x DMAMUX

2 x PIT_RTCAT X

SEMA4

FLEXRAY_1

IIC_1

TDM

PCM

2 x AXBS

EBI

2 x XBIC

TSENS

PSI5_S_0

Loading...

Loading...