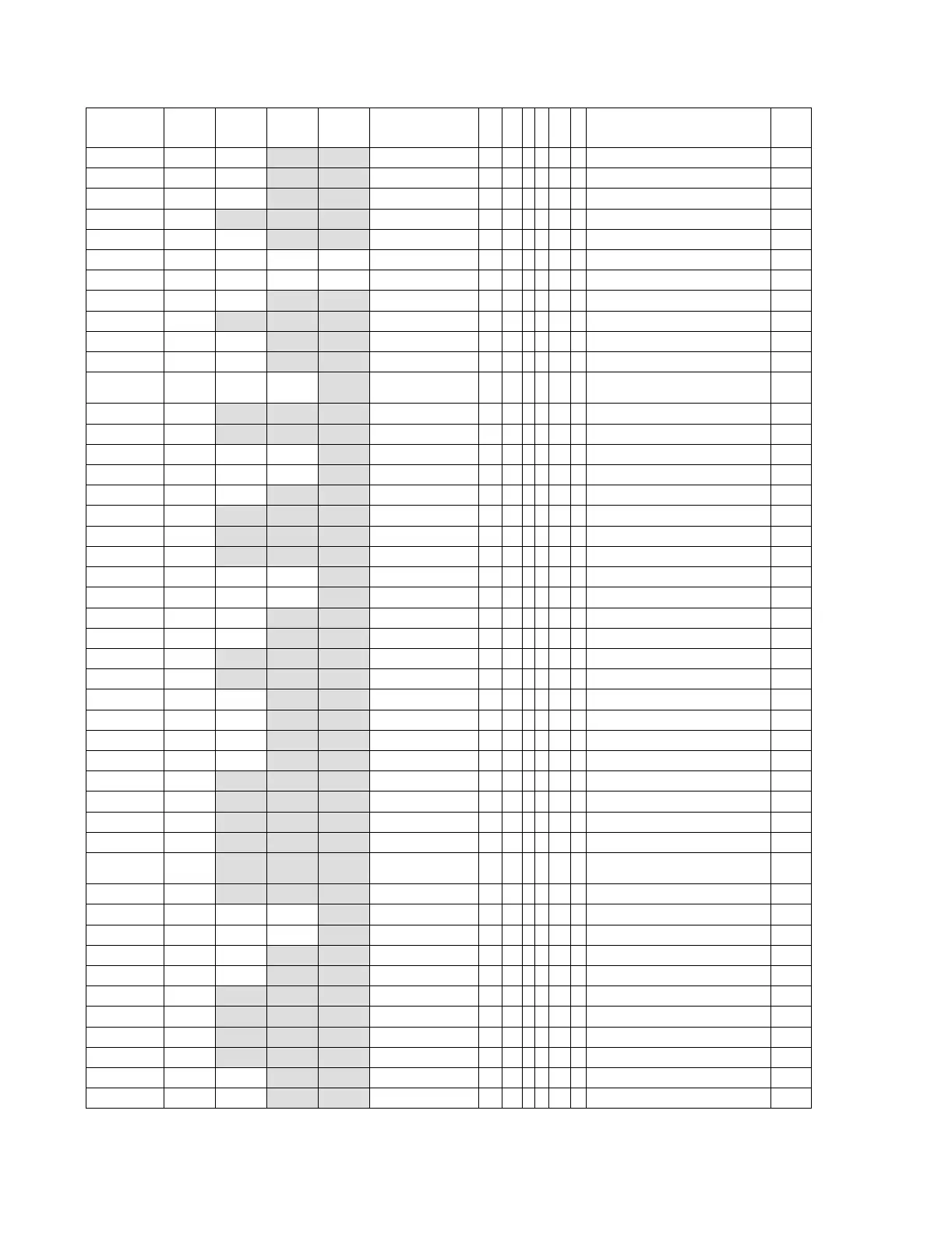

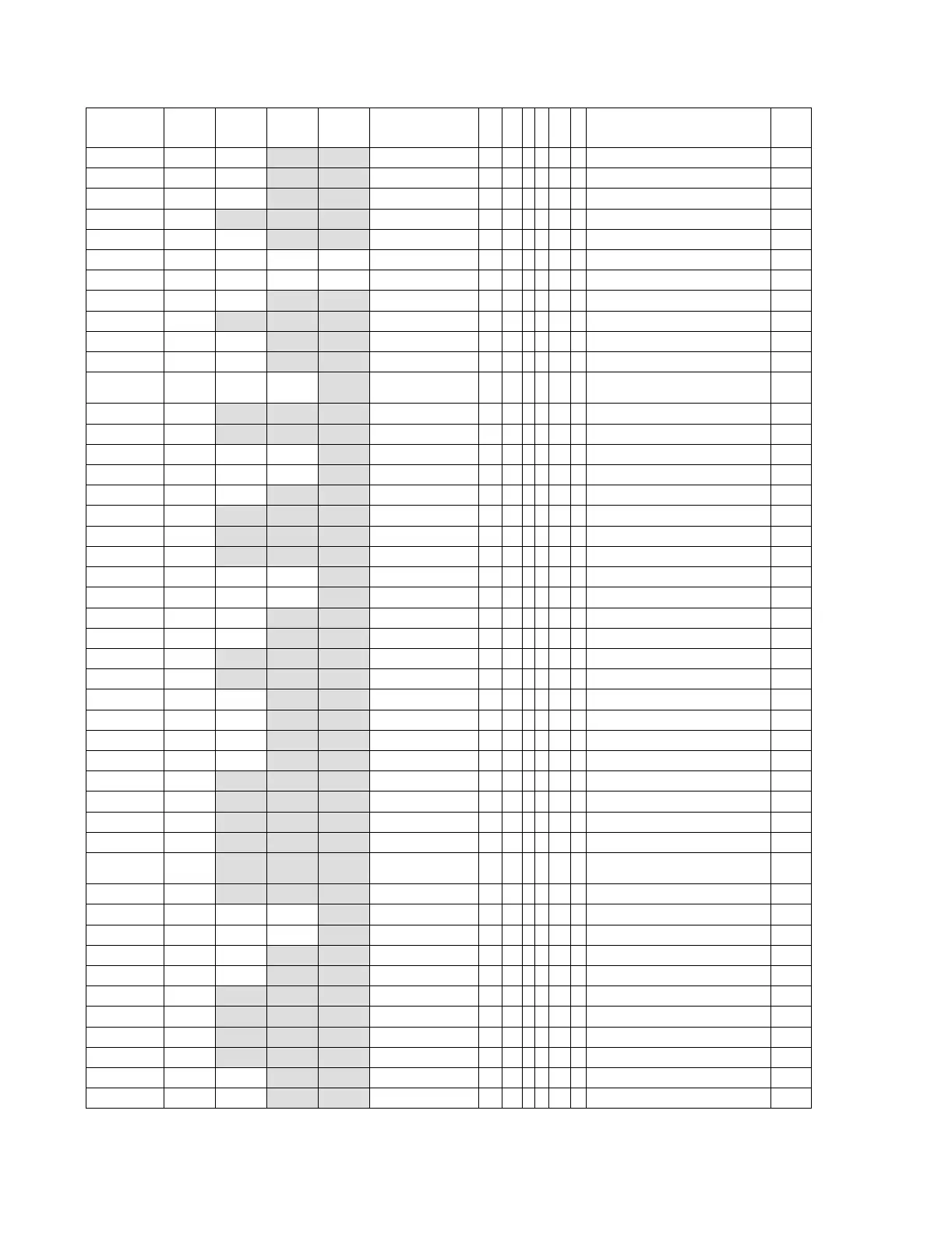

162 Rabbit 2000/3000 Microprocessor

AND IX,DE 11011101 11011100 4(2,2) f * * L 0 IX=IX&DE N

AND IY,DE 11111101 11011100 4(2,2) f * * L 0 IY=IY&DE N

AND n 11100110 ----n--- 4(2,2) fr * * L 0 A=A&n

AND r 10100-r- 2 fr * * L 0 A=A&r

BIT b,(HL) 11001011 01-b-110 7 (2,2,1,2) f s - * - - (HL) & bit P

BIT b,(IX+d) 11011101 11001011 ----d--- 01-b-110 10 (2,2,2,2,2) f s - * - - (IX+d) & bit

BIT b,(IY+d) 11111101 11001011 ----d--- 01-b-110 10 (2,2,2,2,2) f s - * - - (IY+d) & bit

BIT b,r 11001011 01-b--r- 4(2,2) f - * - - r&bit

BOOL HL 11001100 2 fr * * 0 0 if (HL != 0) HL = 1 N

BOOL IX 11011101 11001100 4(2,2) f * * 0 0 if(IX!=0)IX=1 N

BOOL IY 11111101 11001100 4(2,2) f * * 0 0 if(IY!=0)IY=1 N

CALL mn 11001101 ----n--- ----m--- 12 (2,2,2,3,3) - - - -

(SP-1) = PCH; (SP-2) = PCL;

PC = mn; SP = SP-2

CCF 00111111 2 f - - - * CF = ~CF

CP (HL) 10111110 5 (2,1,2) f s * * V * A-(HL)

CP (IX+d) 11011101 10111110 ----d--- 9 (2,2,2,1,2) f s * * V * A-(IX+d)

CP (IY+d) 11111101 10111110 ----d--- 9 (2,2,2,1,2) f s * * V * A-(IY+d)

CP n 11111110 ----n--- 4(2,2) f * * V * A-n

CP r 10111-r- 2 f * * V * A-r

CPL 00101111 2 r - - - - A=~A

DEC (HL) 00110101 8 (2,1,2,3) f b * * V - (HL) = (HL) - 1

DEC (IX+d) 11011101 00110101 ----d--- 12 (2,2,2,1,2,3) f b * * V - (IX+d) = (IX+d) -1

DEC (IY+d) 11111101 00110101 ----d--- 12 (2,2,2,1,2,3) f b * * V - (IY+d) = (IY+d) -1

DEC IX 11011101 00101011 4(2,2) - - - - IX = IX - 1

DEC IY 11111101 00101011 4(2,2) - - - - IY = IY - 1

DEC r 00-r-101 2 fr * * V - r=r-1

DEC ss 00ss1011 2 r - - - - ss = ss - 1

DJNZ e 00010000 --(e-2)- 5 (2,2,1) r - - - - B = B-1; if {B != 0} PC = PC + e

EX (SP),HL 11101101 01010100 15 (2,2,1,2,2,3,3) r - - - - H <-> (SP+1); L <-> (SP) M

EX (SP),IX 11011101 11100011 15 (2,2,1,2,2,3,3) - - - - IXH <-> (SP+1); IXL <-> (SP)

EX (SP),IY 11111101 11100011 15 (2,2,1,2,2,3,3) - - - - IYH <-> (SP+1); IYL <-> (SP)

EX AF,AF’ 00001000 2 - - - - AF <-> AF'

EX DE,HL 11101011 2 s - - - - if (!ALTD) then DE <-> HL else DE <-> HL' N

EX DE’,HL 11100011 2 s - - - - if (!ALTD) then DE' <-> HL else DE' <-> HL'

EXX 11011001 2 - - - - BC <-> BC'; DE <-> DE'; HL <-> HL'

IDET 01011011 2 - - - -

E = E, but if (EDMR && SU[0])

then System Violation interrupt flag is set

INC (HL) 00110100 8 (2,1,2,3) f b * * V - (HL) = (HL) + 1

INC (IX+d) 11011101 00110100 ----d--- 12 (2,2,2,1,2,3) f b * * V - (IX+d) = (IX+d) + 1

INC (IY+d) 11111101 00110100 ----d--- 12 (2,2,2,1,2,3) f b * * V - (IY+d) = (IY+d) + 1

INC IX 11011101 00100011 4(2,2) - - - - IX = IX + 1

INC IY 11111101 00100011 4(2,2) - - - - IY = IY + 1

INC r 00-r-100 2 fr * * V - r=r+1

INC ss 00ss0011 2 r - - - - ss = ss + 1

IOE 11011011 2 - - - - I/O external prefix N

IOI 11010011 2 - - - - I/O internal prefix N

IPSET 0 11101101 01000110 4(2,2) - - - - IP = {IP[5:0], 00} NP

IPSET 1 11101101 01010110 4(2,2) - - - - IP = {IP[5:0], 01} NP

Instruction

Opcode

byte 1

Opcode

byte 2

Opcode

byte 3

Opcode

byte 4

Clock cycles A I S Z LV C Operation N/M/P

Loading...

Loading...