Multiply Halfword

(MH)

General

Description

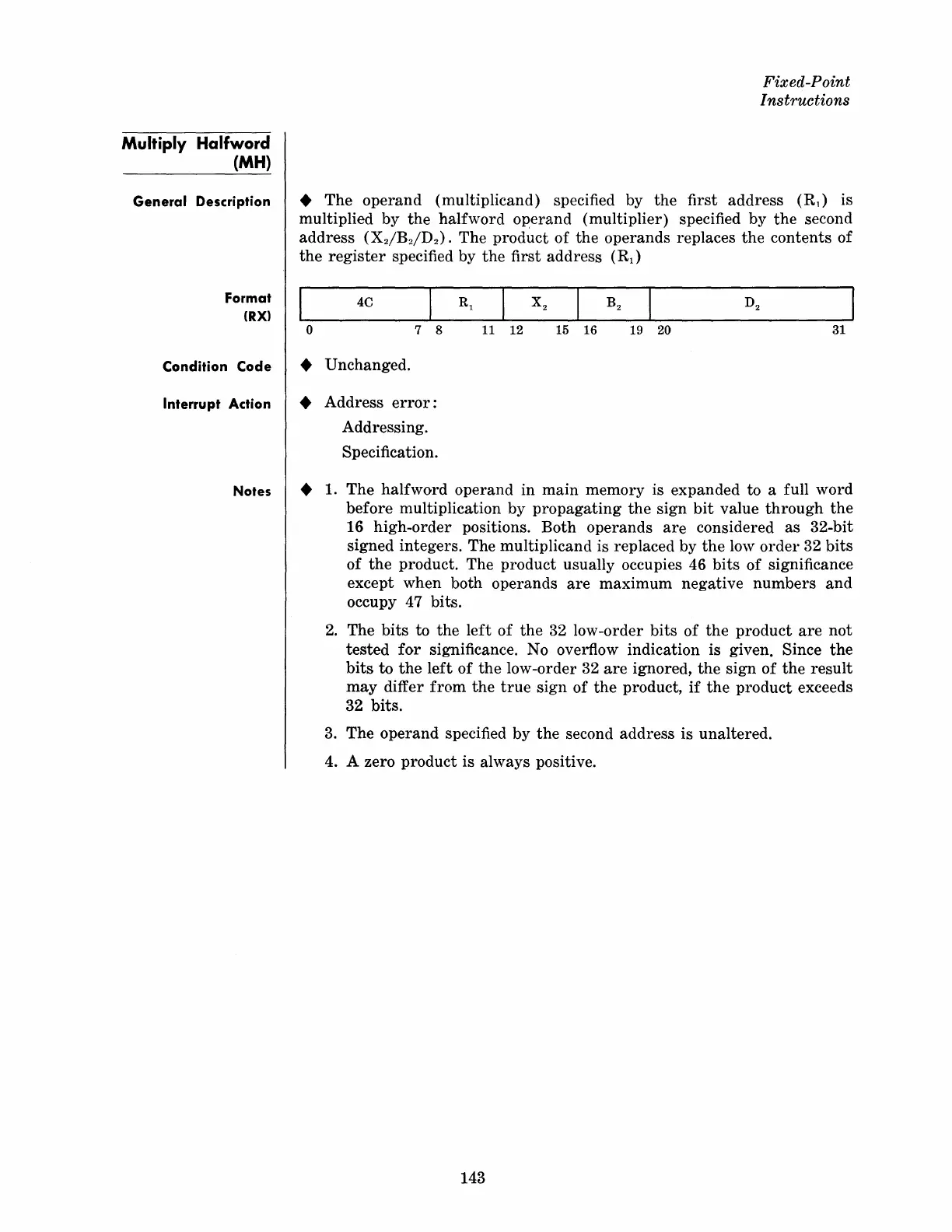

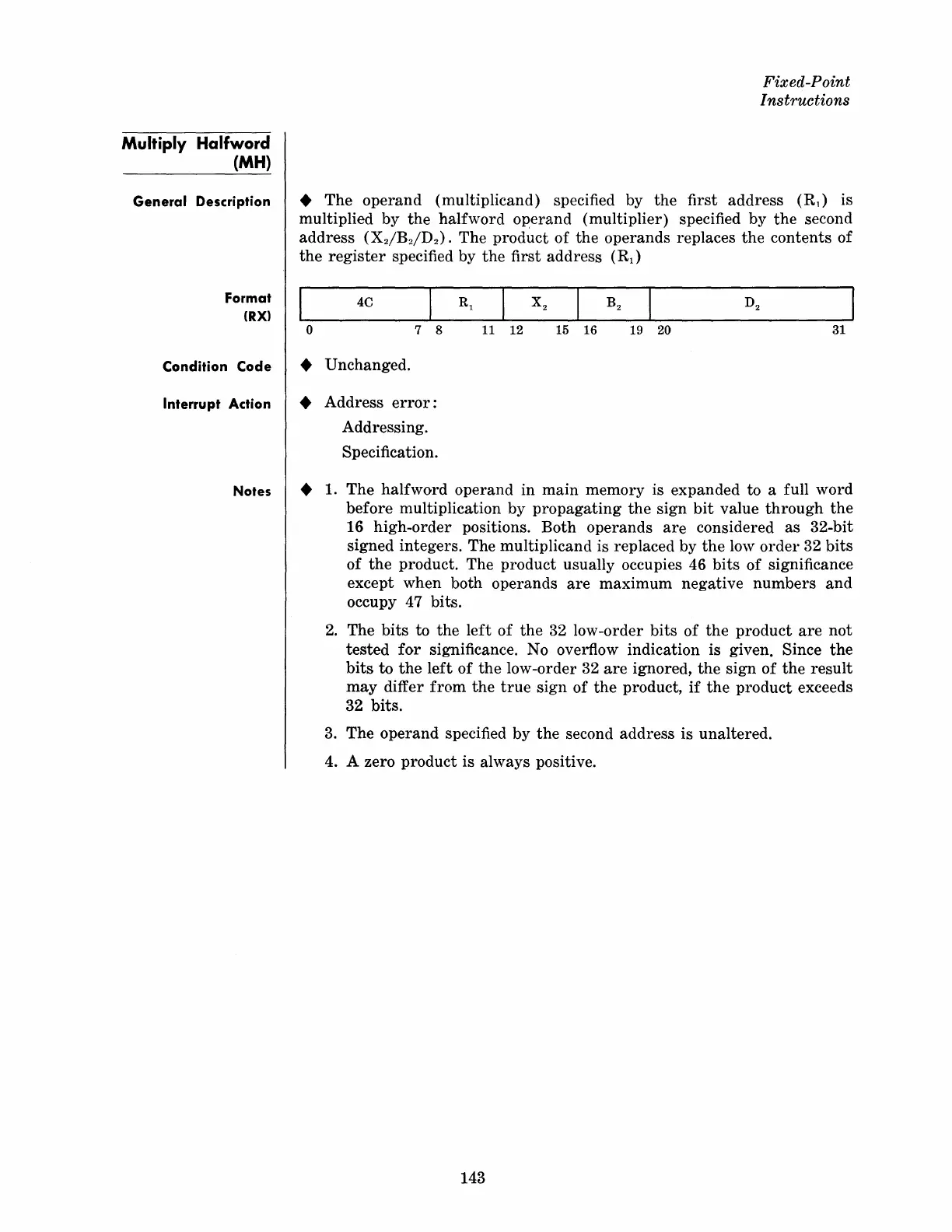

Format

(RX)

Condition Code

Interrupt

Action

Notes

Fixed-Point

Instructions

•

The

operand

(multiplicand) specified by

the

first

address

(R

1

)

is

multiplied

by

the

halfword

operand (multiplier) specified

by

the

second

address

(XdB

2

/D

2

).

The

product

of

the

operands replaces

the

contents

of

the

register

specified by

the

first

address

(R

1

)

o

7 8 11 12 15 16 19 20

31

• Unchanged.

•

Address

error:

Addressing.

Specification.

• 1.

The

halfword

operand in

main

memory is expanded to a full

word

before

multiplication by

propagating

the

sign

bit

value

through

the

16

high-order

positions.

Both

operands

are

considered

as

32-bit

signed integers. The multiplicand is replaced by

the

low

order

32

bits

of

the

product. The

product

usually occupies 46

bits

of

significance

except when both operands

are

maximum

negative

numbers

and

occupy 47 bits.

2.

The

bits

to

the

left

of

the

32 low-order

bits

of

the

product

are

not

tested

for

significance. No overflow indication is given. Since

the

bits

to

the

left

of

the

low-order 32

are

ignored,

the

sign

of

the

result

may

differ

from

the

true

sign

of

the

product,

if

the

product

exceeds

32 bits.

3.

The

operand specified by

the

second

address

is unaltered.

4. A zero

product

is always positive.

143

Loading...

Loading...