TPS-1 User’s Manual: Hardware 7. TPS-1 Watchdog

R19UH0081ED0107 Rev. 1.07 page 49 of 86

Jul 30, 2018

7. TPS-1 Watchdog

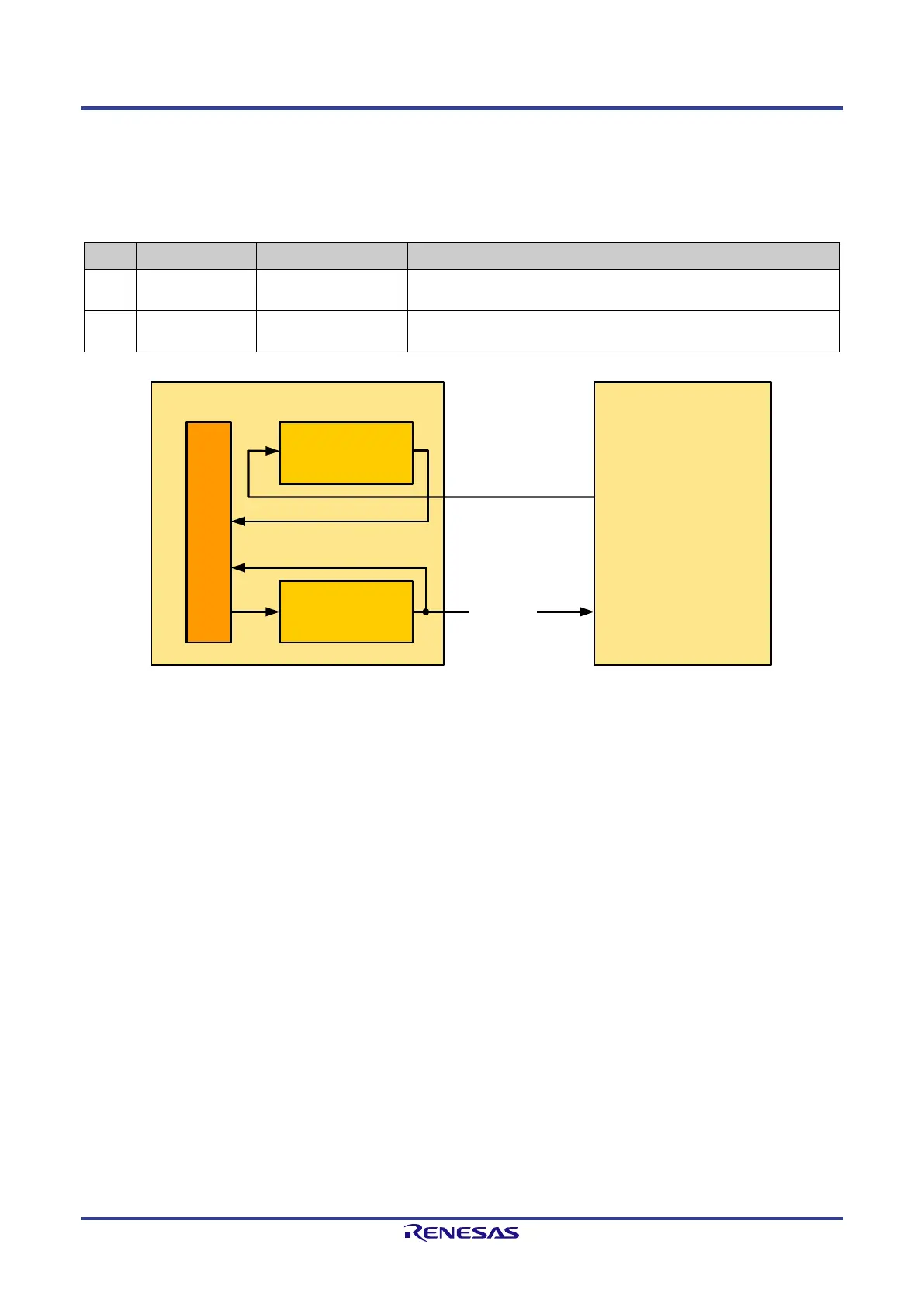

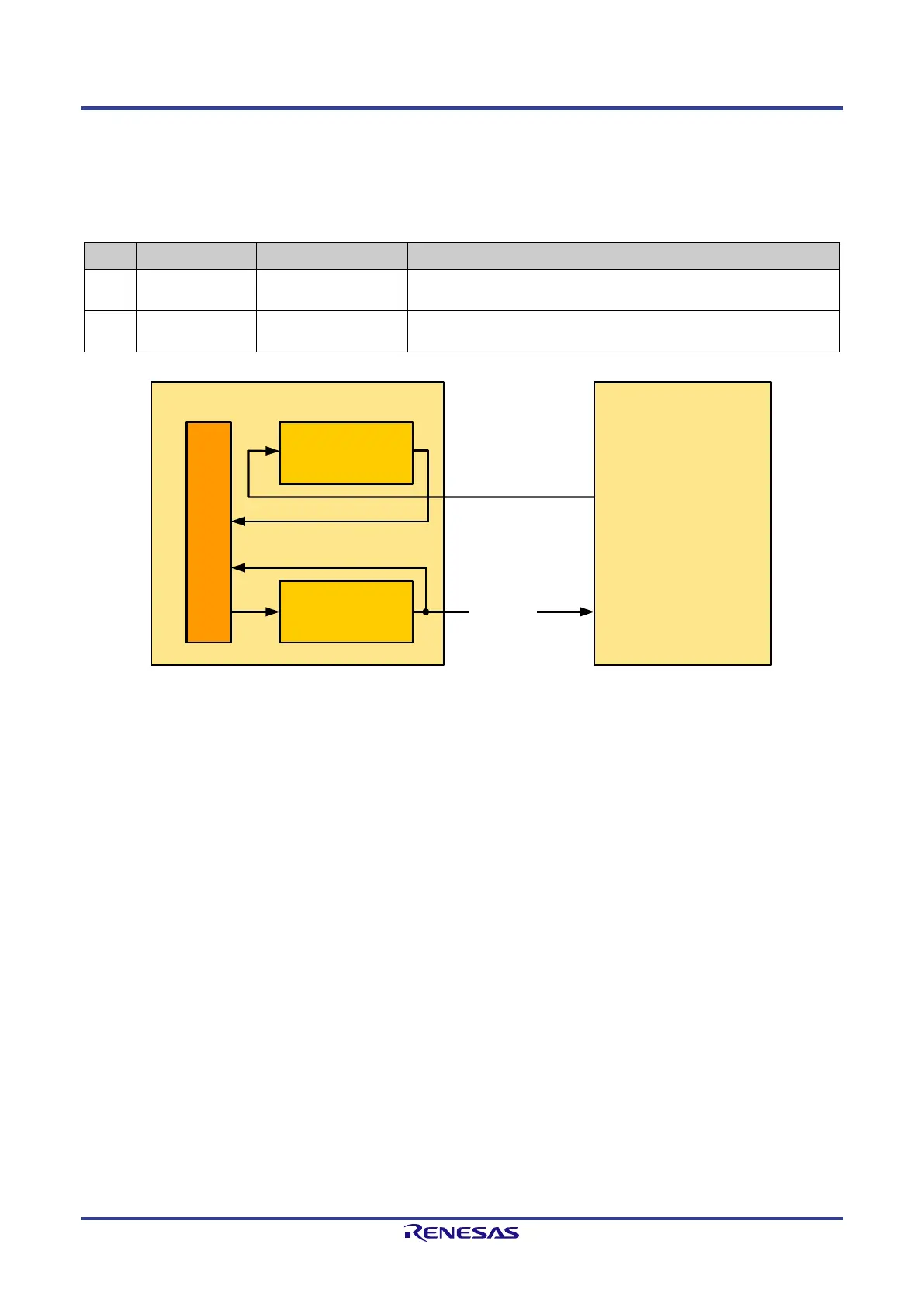

The TPS-1 contains two watchdog controllers. One is used to control the PROFINET CPU. The other shall be used to control the connected Host CPU.

The signals WD_IN and WD_OUT are used by the host CPU and the TPS-1 for mutual supervision and to force a restart if necessary.

Table 7-1: Watchdog signals

Pin Signal TPS-1 Description Remark

A11 WD_IN Watchdog Input

(from the Host)

This signal triggers the TPS-1 watchdog that monitors the Host

CPU. A rising edge of this signal restarts the watchdog counter.

(to the Host)

This signal is set when a watchdog trigger of the TPS-1 occurs

(active low).

TPS

-1 Host CPU

WD_OUT

Watchdog 0

Watchdog 1

WD_IN

ExtTrigger

ExtTrigger

TPS-CPU

CPU RESET

CPU Interrupt

Figure 7-1: TPS-1 Watchdog Lines

7.1. Signal WD_OUT (pin B12)

The WD_OUT signal is processed by the TPS-1. The TPS-1 starts its watchdog during start up (the signal is set to high level during power up). This is

done by the TPS-1 firmware

The signal WD_OUT indicates that a watchdog error occurs inside the TPS-1.

A watchdog error forces the TPS-1 to a reset. All communication connections to a controller are dropped down.

After a restart of the TPS-1, the host must configure the TPS-1 again.

If you are using the HOST-Interface, the external CPU must guarantee a secure behavior of the process output signals in case of a TPS-

1 Watchdog.

In case of using the local IO interface, additional circuitry must avoid insecure signals for process outputs.

Loading...

Loading...