TPS-1 User’s Manual: Hardware 2. Pin function

R19UH0081ED0107 Rev. 1.07 page 14 of 86

Jul 30, 2018

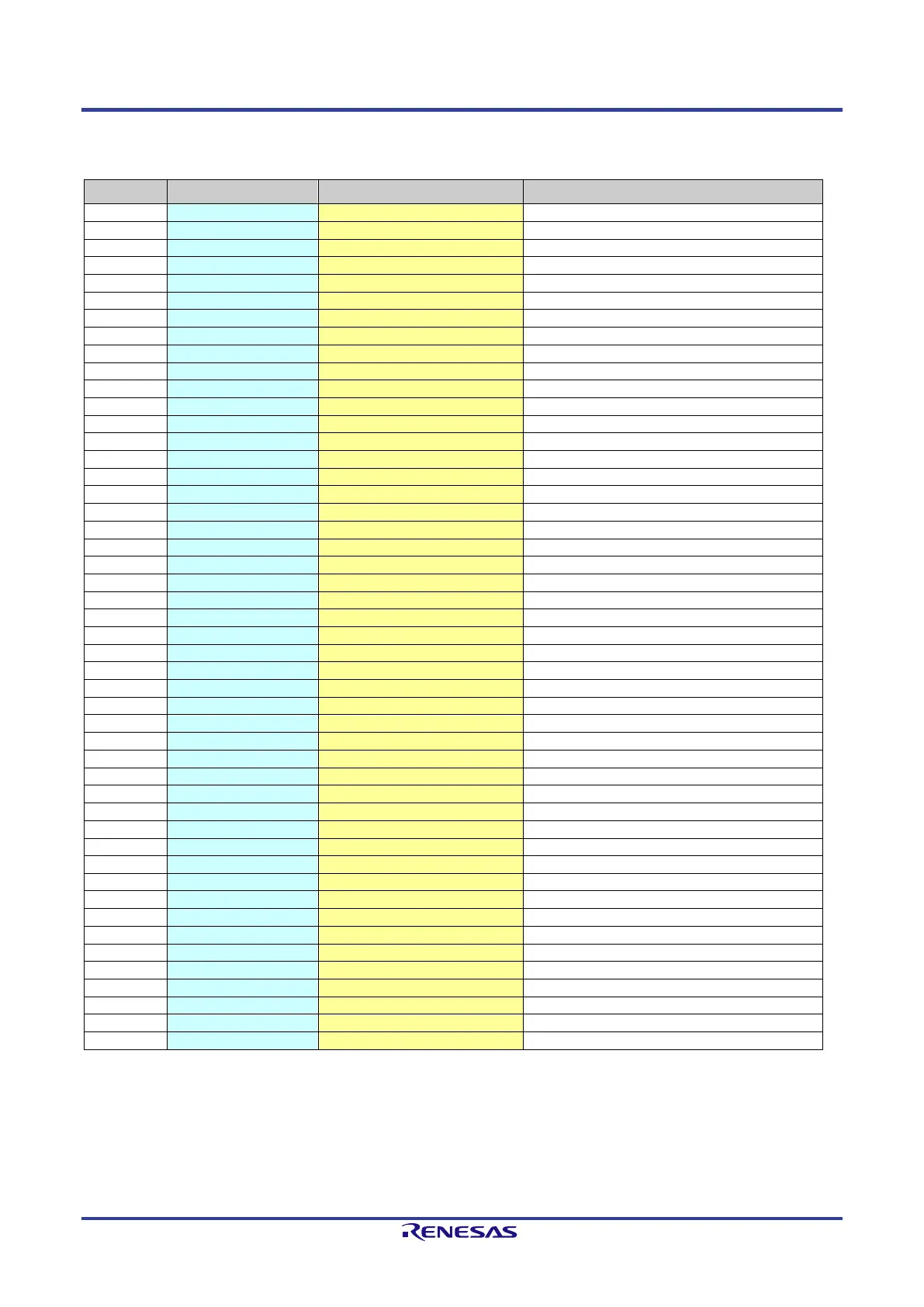

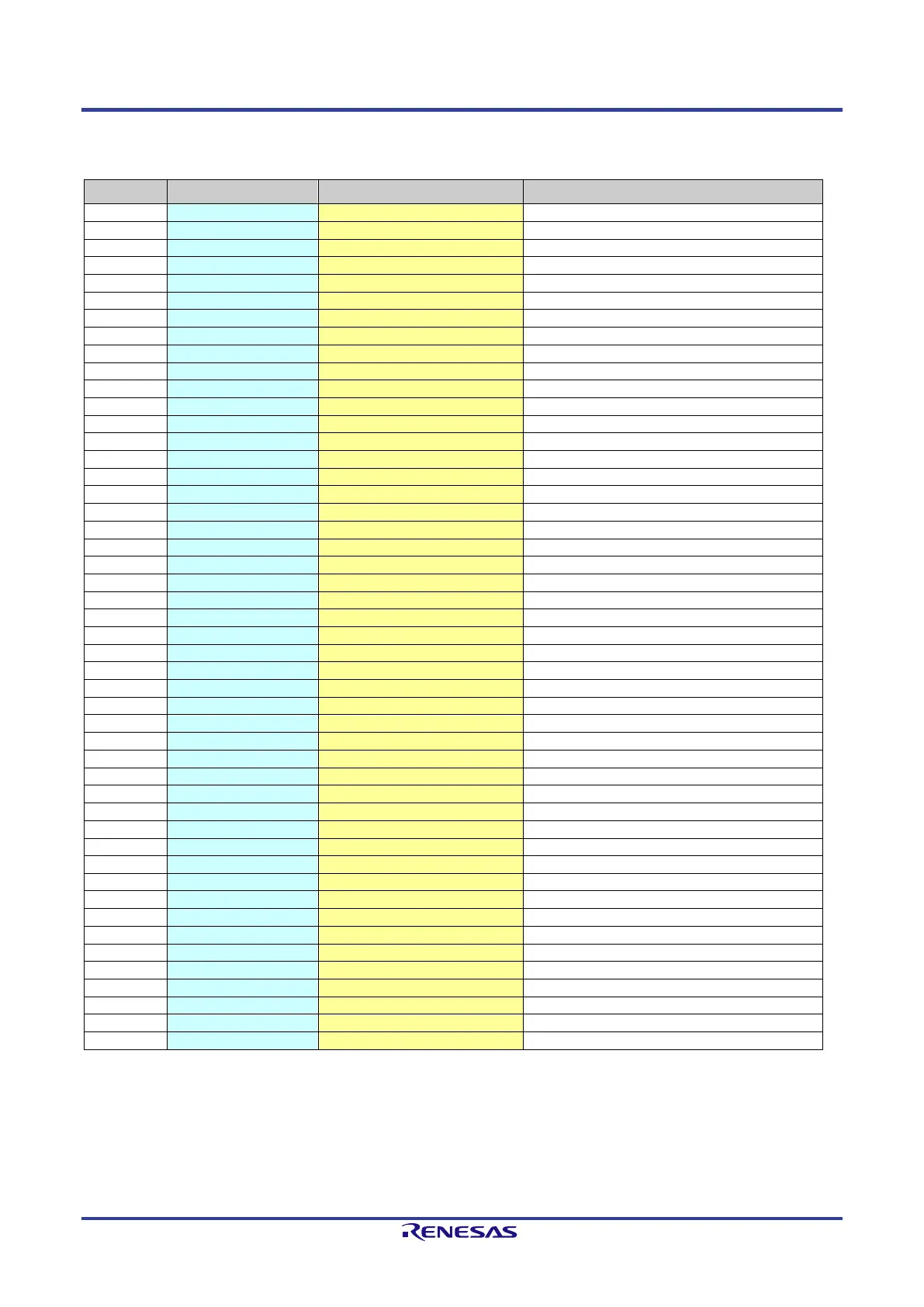

2.2. GPIO multiplexing

Table 2-2: Alternate use of the GPIOs

Ready Signal TPS-1 (Note 1), (Note 2)

Start new SPI Transfer (Note 3)

SPI Clock (SPI master IO interface)

SPI Chip Select (SPI master IO interface)

SPI receive date (SPI master IO interface)

SPI transmit data (SPI master IO interface)

Note: You can only use one interface exclusively. It is not allowed to use e.g. the parallel and serial host interface at the same time.

Note 1): The “LBU_READY_OUT” is designed to connect only to one microcontroller. If you want to connect additional devices you must

add circuitry to realize the high-impedance state.

Note 2): If your processor does not have a READY Input, you can choose a wait time of 260 ns during each transfer cycle.

Note 3): As soon as the signal HOST_SFRN_IN is set to “1”, no more data is received on the RxD interface. Setting the signal is not allowed

during an ongoing transfer.

Loading...

Loading...