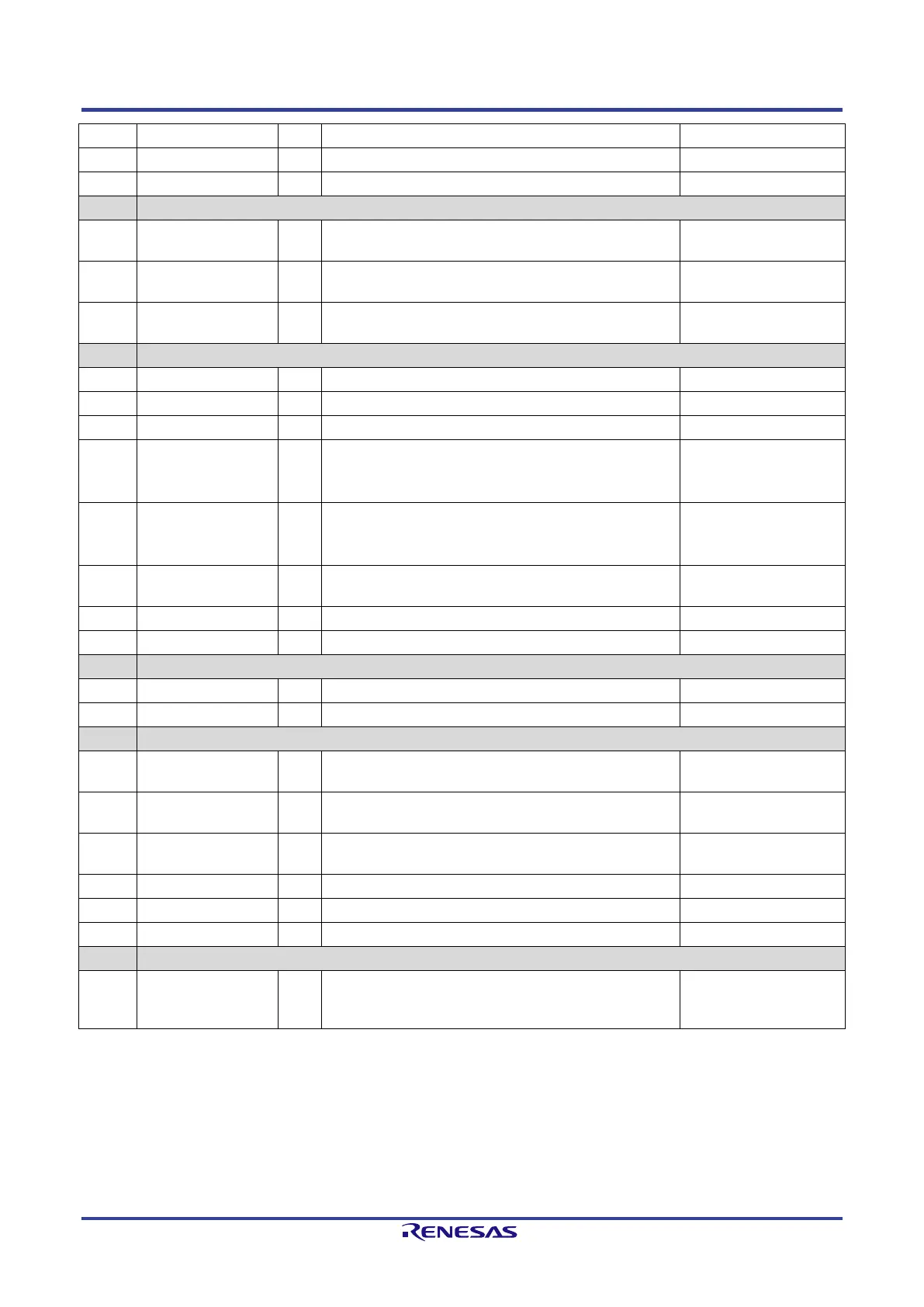

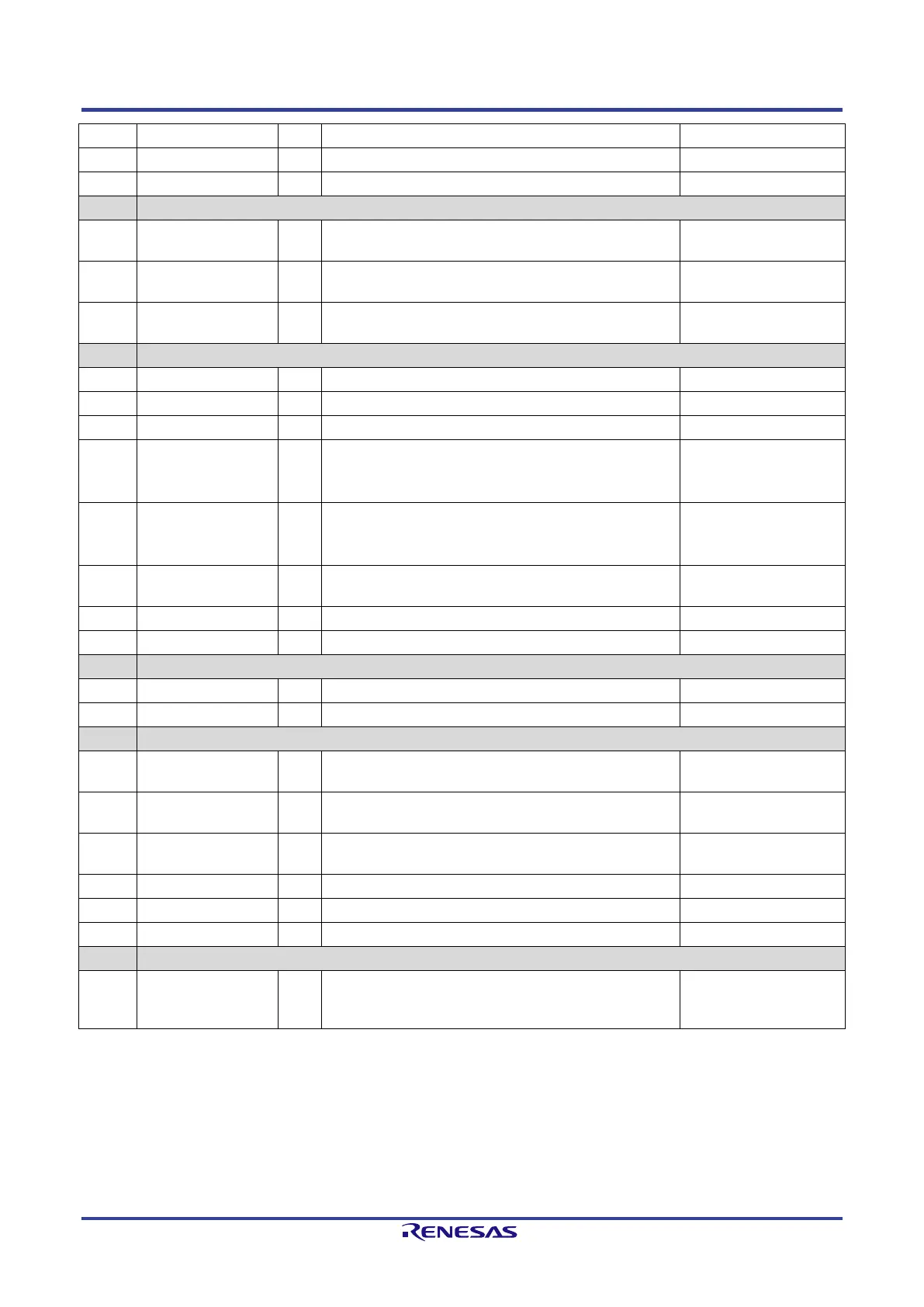

TPS-1 User’s Manual: Hardware 2. Pin function

R19UH0081ED0107 Rev. 1.07 page 13 of 86

Jul 30, 2018

C14 UART6_TX O Boot UART “Transmit Data“

P12 BOOT_1 I Forced Boot

Test signals for switching regulator

H3 TEST1 I Test Pin switching regulator (in combination with

Test2, Test3)

Test Pin switching regulator (in combination with

Test1, Test3)

E1 TEST3 I Test Pin switching regulator (in combination with

Test1, Test2)

E12 VDD33ESD Analog test supply, 3.3 V

PECL buffer power supply 3.3 V (Port 1)

M8 VDDQ_PECL_B2 I PECL buffer power supply 3.3 V (Port 2)

D14 P1VDDARXTX I Analog Rx/Tx port power supply

Analog 1.5 V V

DD

(must be generated via a filter from

digital 1.5 V power supply) – Port 1

L14 P2VDDARXTX I Analog Rx/Tx port power supply

Analog 1.5 V V

DD

(must be generated via a filter from

digital 1,5 V power supply) – Port 2

H14 VDDACB I Analog 3.3 V V

DD

(must be generated via a filter from

digital 3.3 V power supply)

G13 VSSAPLLCB Analog central GND

G14 VDDAPLL Analog central power supply for PHYs, 1.5 V

Pins for core PLL power supply

(core PLL)

L10 PLL_AVDD PLL analog 1.0 V (core PLL)

Pins for switching regulator

J1 BVDD I Supply voltage for the switching regulator (3.3 V

supply for the switching transistor)

GND for switching regulator (please place bypass

capacitor between analog power supply and GND).

F2 AVDD_REG Analog VDD for regulator (3.3 V supply),

smoothed voltage to feed the internal POR.

Note 1)

Analog GND switching regulator

H1 LX O 1.5 V output of the internal switching regulator

Configurable GPIOs

GPIO_47

(see table “Alternate use of the GPIO”)

After reset the GPIO pin are configured as Inputs (no

pull up or down)

Notes:

1. Pin F2 must be always connected to VDD33 (refer Figure 8-2: Internal voltage regulator).

2. The signal TEST_SYNC must be available for certification test (a reachable pad is enough).

Loading...

Loading...