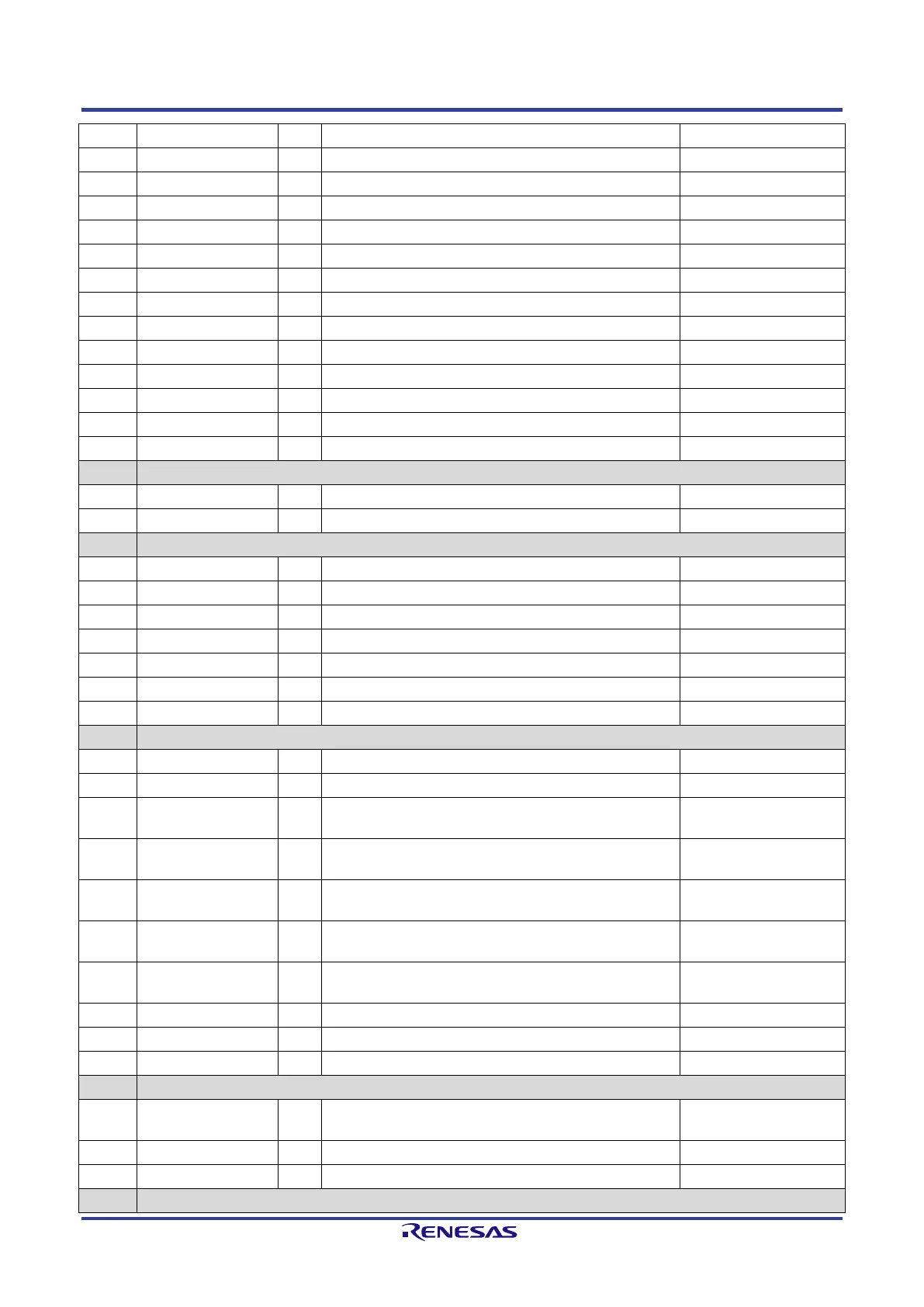

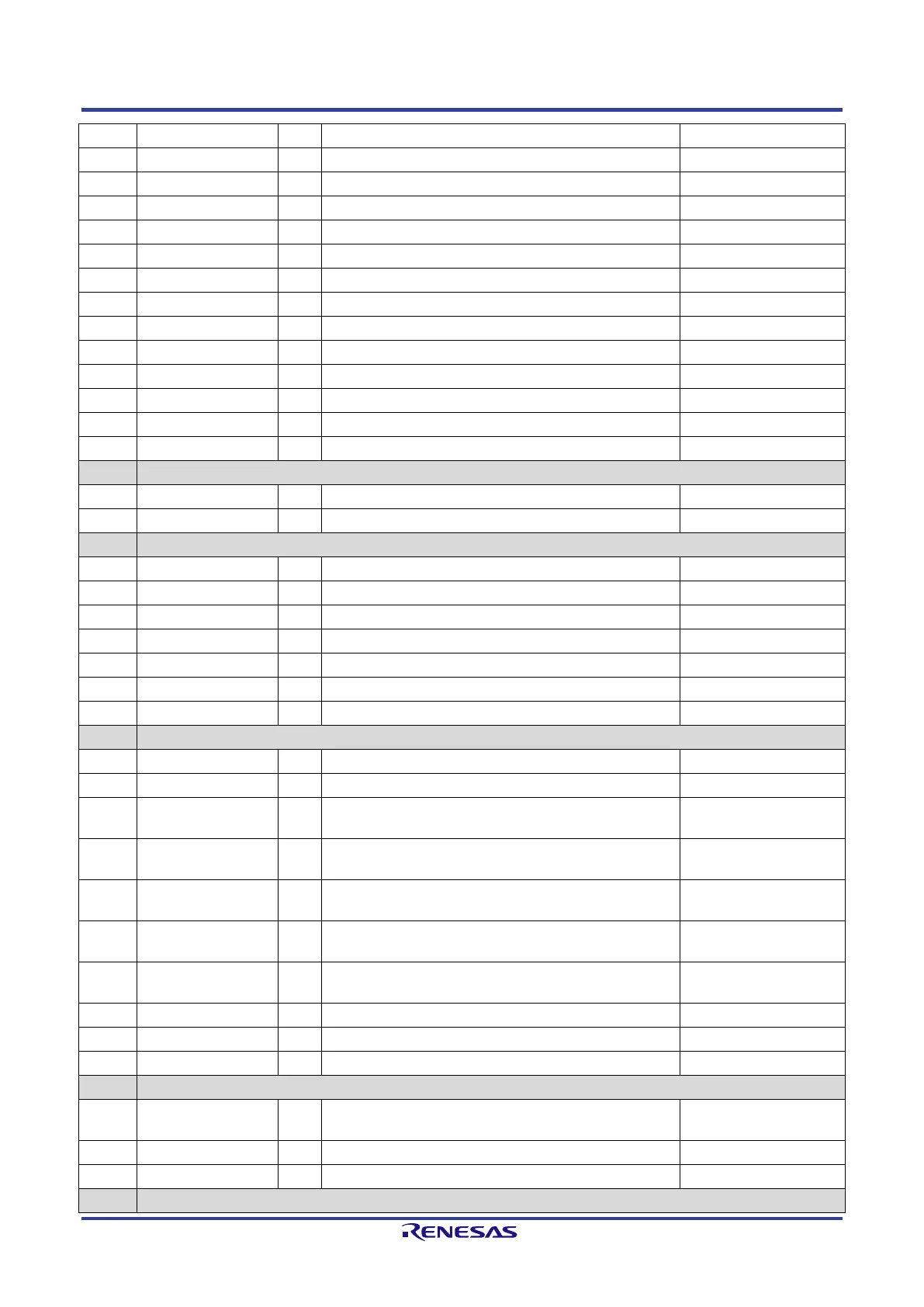

TPS-1 User’s Manual: Hardware 2. Pin function

R19UH0081ED0107 Rev. 1.07 page 12 of 86

Jul 30, 2018

L11 SCLK_2_INOUT O Fiber Optic Port 2: I

2

C-Bus “Clock” e.g. SC-RJ

LINK indication ETHERNET Port 2 (up or down)

A10 ACT_PHY2 O Activity ETHERNET Port 2 (active high)

ETHERNET Port 2 Transmit Data (positive)

J14 P2_TX_N O ETHERNET Port 2 Transmit Data (negative) e.g. RJ45

K13 P2_RX_P I ETHERNET Port 2 Receive Data (positive) e.g. RJ45

ETHERNET Port 2 Receive Data (negative)

Fiber Optic Port 2: Signal Detect (positive)

P8 P2_SD_N I Fiber Optic Port 2: Signal Detect (negative) e.g. SC-RJ

Fiber Optic Port 2: Receive Data (positive)

P9 P2_RD_N I Fiber Optic Port 2: Receive Data (negative) e.g. SC-RJ

N6 P2_TD_OUT_P O Fiber Optic Port 2: Transmit Data (negative) e.g. SC-RJ

Fiber Optic Port 2: Transmit Data (positive)

Fiber Optic Port 2: Transmitter enable (active high)

Oscillator

Connection external oscillator (1), 25 MHz

P11 XCLK2 O Connection external oscillator (2), 25 MHz

L4 TM0 I Test Input 0 (Chip Test - 10k to GND) (pull down external)

Test Input 1 (Chip Test - 10k to GND)

K5 TRSTN I JTAG-Interface: “Test Reset” (pull down external)

JTAG-Interface: “Test Mode Select”

L7 TDO O JTAG-Interface: “Test Data Output”

J5 TCK I JTAG-Interface: “Test Clock” (pull-up external)

JTAG-Interface: “Test Data Input”

A12 RESETN I TPS-1 Reset (Global Reset) (active low)

Test pin for production test (n.c.)

H13 EXTRES O External reference resistor (12.4 kΩ,1 %), connect to

analog GND

Test Mode Control 1 (production test)

recommended)

K10 TMC2 I Test Mode Control 2 (production test) (pull down external

recommended)

Test Pin 1 for hardware test of the TPS-1

recommended)

D7 TEST_2_IN I Test Pin 2 for hardware test of the TPS-1 (pull down external

recommended)

Test Data Output 5 (High Speed Signals for PHY)

Test Data Output 6 (High Speed Signals for PHY)

Test Data Output 7 (High Speed Signals for PHY)

Host interface

Watchdog input (from the Host) (the rising edge resets

the watchdog counter of the TPS-1)

B12 WD_OUT O Watchdog output (to the Host) (active low)

Interrupt output (to the Host)

Boot interface (serial)

Loading...

Loading...