Technical data of CPU 31xC

6.5 CPU 314C-2 PtP and CPU 314C-2 DP

CPU 31xC and CPU 31x, Technical data

6-22 Manual, Edition 08/2004, A5E00105475-05

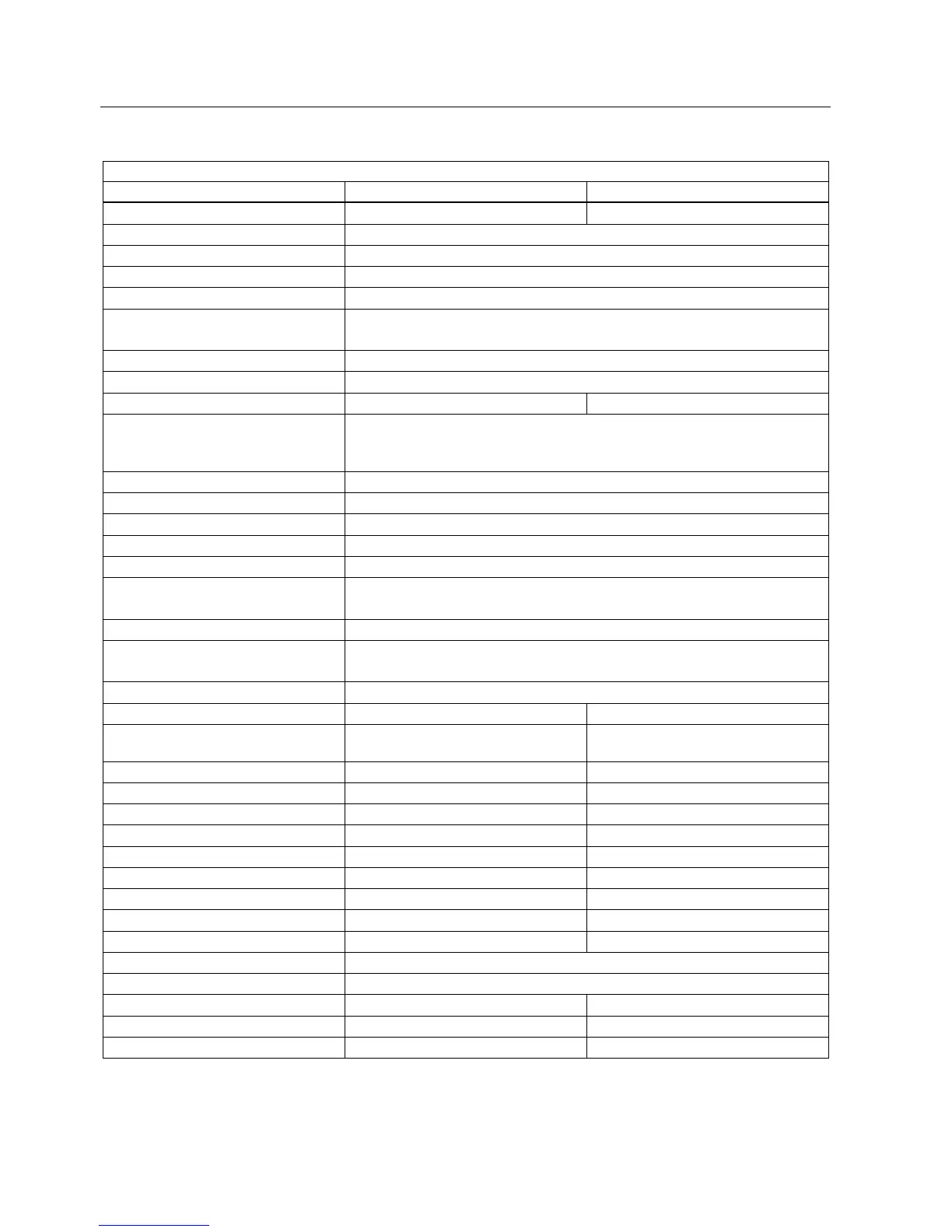

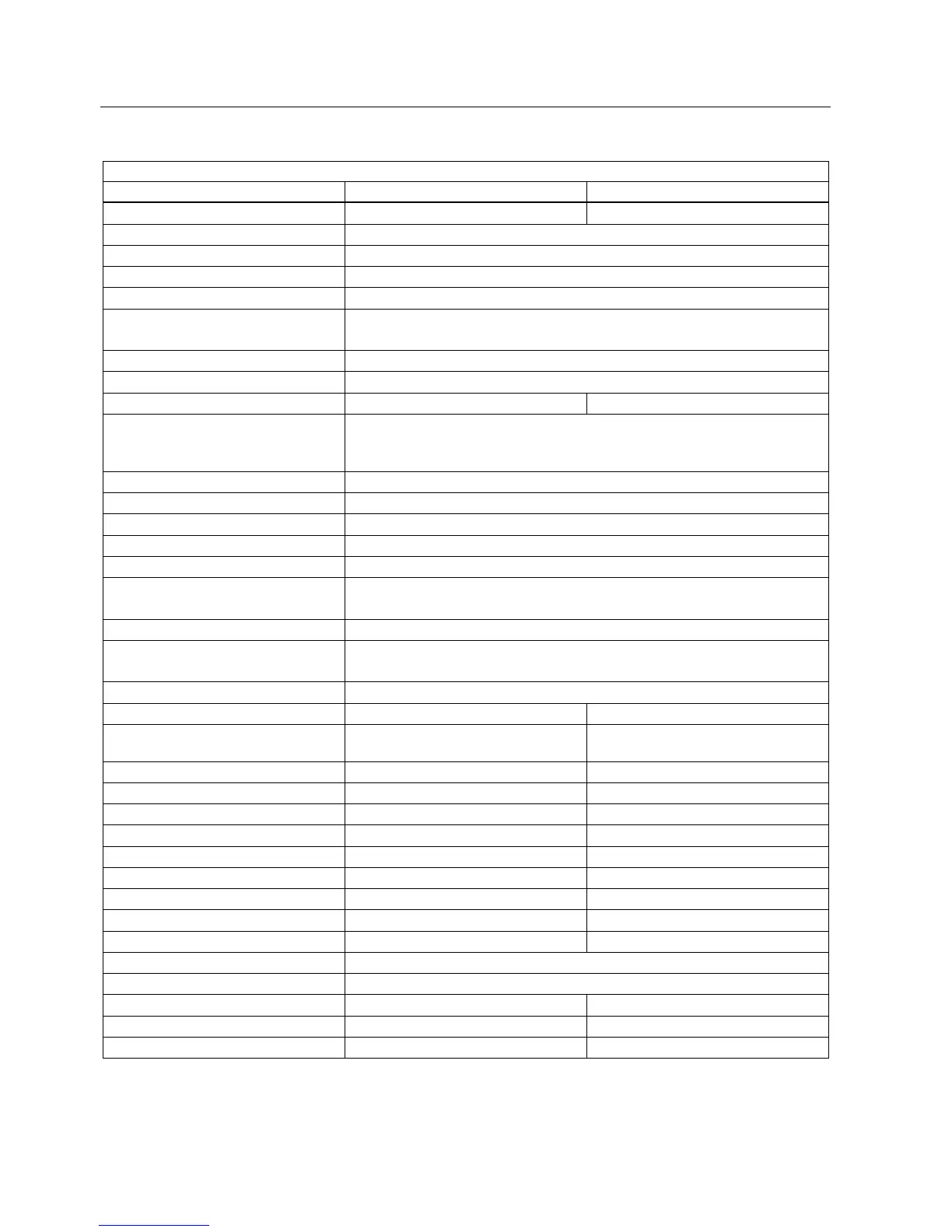

Technical data

CPU 314C-2 PtP CPU 314C-2 DP

Data areas and their retentivity CPU 314C-2 PtP CPU 314C-2 DP

Flag bits 256 bytes

• Retentive memory

Configurable

• Default retentivity

MB0 to MB15

Clock flag bits 8 (1 byte per flag bit)

Data blocks Max. 511

(DB 1 to DB 511)

• Length

max. 16 KB

Local data per priority class max. 510 bytes

Blocks CPU 314C-2 PtP CPU 314C-2 DP

Total 1024 (DBs, FCs, FBs)

The maximum number of blocks that can be loaded may be reduced if you are

using another MMC.

OBs See the Instruction List

• Length

max. 16 KB

Nesting depth

• Per priority class

8

• additional within an error OB

4

FBs Max. 512

(FB 0 to FB 511)

• Length

max. 16 KB

FCs Max. 512

(FC 0 to FC 511)

• Length

max. 16 KB

Address areas (I/O) CPU 314C-2 PtP CPU 314C-2 DP

Total I/O address area max. 1024 bytes/1024 bytes

(can be freely addressed)

max. 1024 bytes/1024 bytes

(can be freely addressed)

• Distributed

None max. 1000 bytes

I/O process image 128 bytes/128 bytes 128 bytes/128 bytes

Digital channels Max. 1016 Max. 8192

• of those local

Max. 992 Max. 992

• Integrated channels

24 DI / 16 DO 24 DI / 16 DO

Analog channels Max. 253 Max. 512

• of those local

Max. 248 Max. 248

• Integrated channels

4 + 1 AI / 2 AO 4 + 1 AI / 2 AO

Assembly CPU 314C-2 PtP CPU 314C-2 DP

Racks Max. 4

Modules per rack max. 8; max. 7 in rack 3

Number of DP masters

• Integrated

No 1

• via CP

Max. 1 Max. 1

Loading...

Loading...