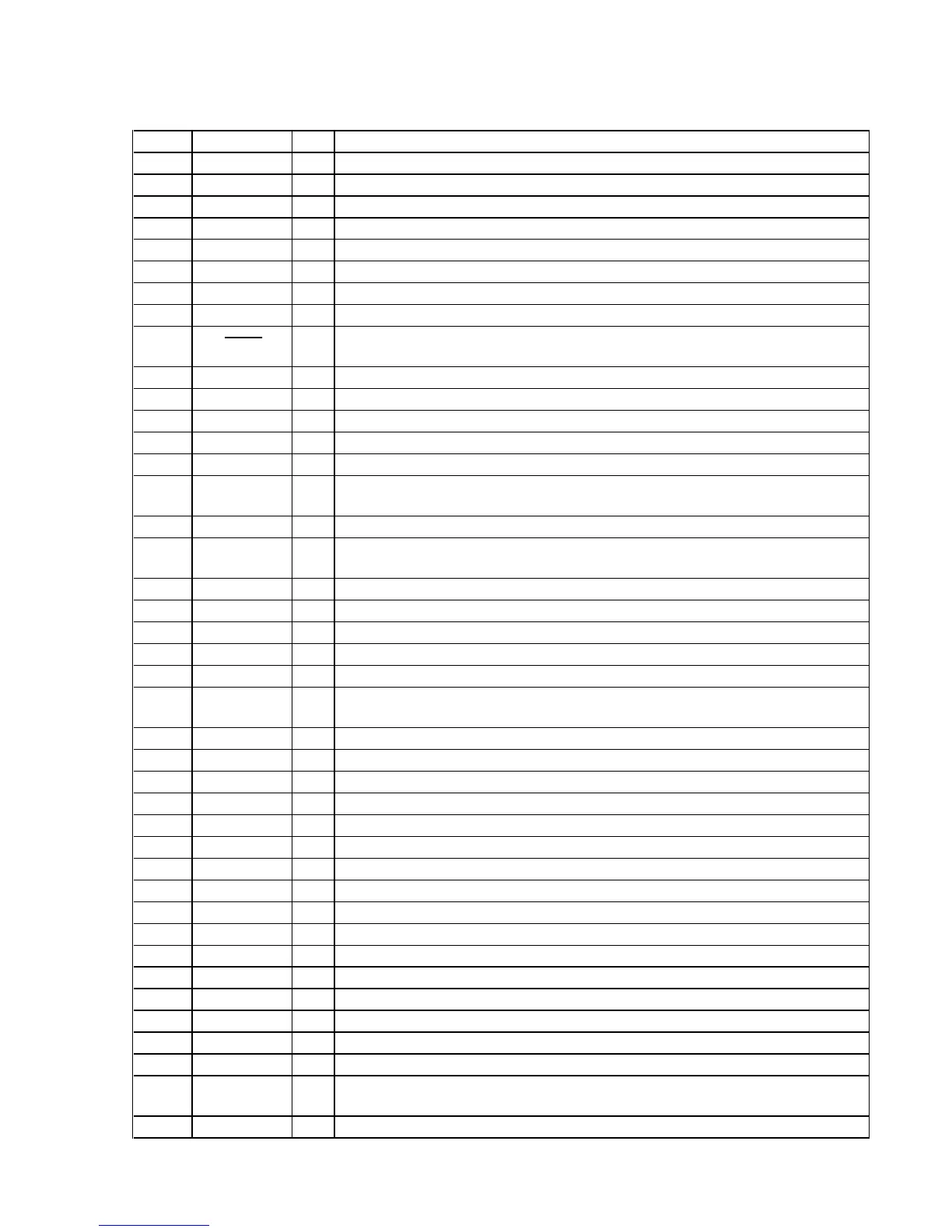

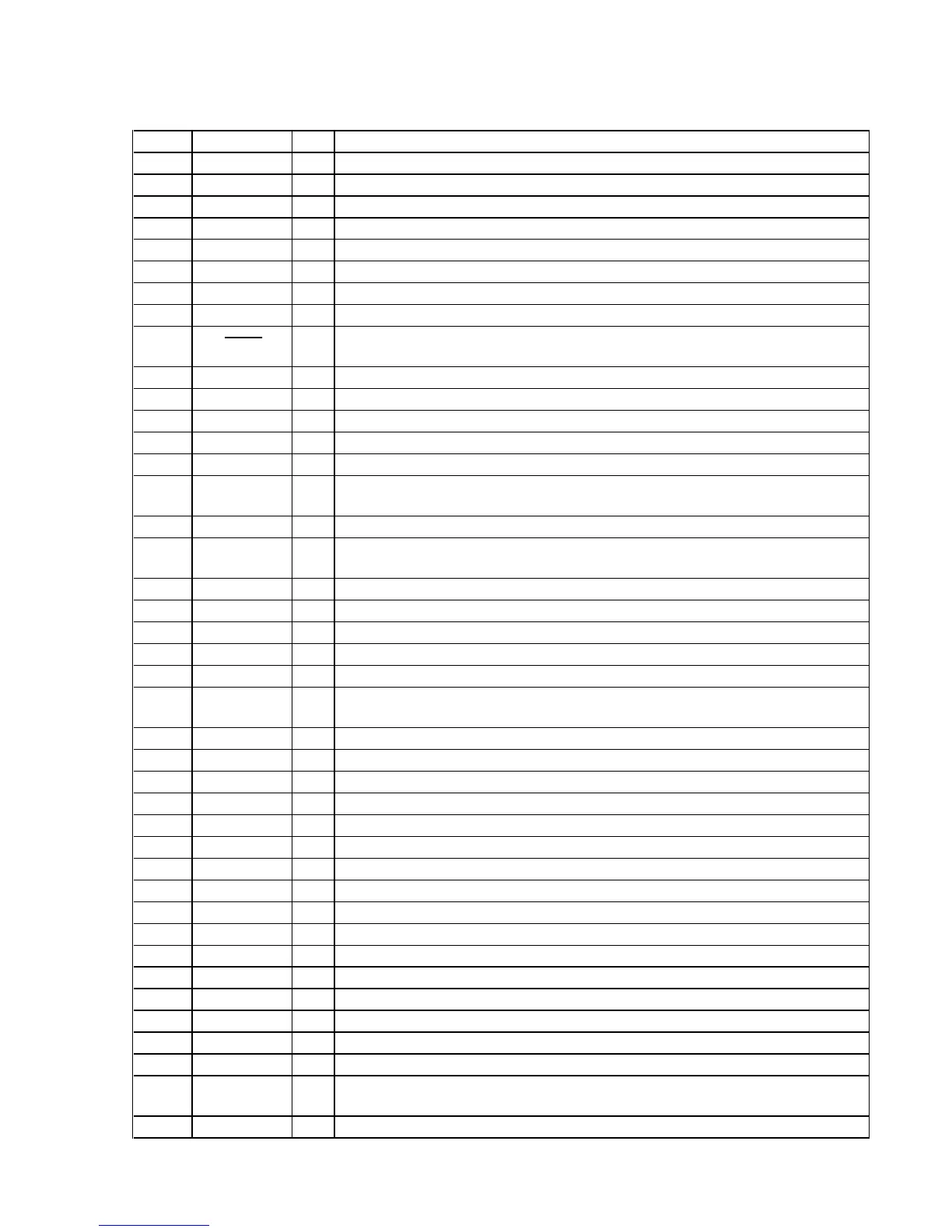

79

MXD-D40

• MAIN BOARD IC801 M30803MG (MD MECHANISM CONTROLLER)

Pin No. Pin Name I/O Description

1, 2 NC

O Not used (open)

3 LEVEL_L

O L-ch level output to the CD mechanism controller (IC800)

4 LEVEL_R

O R-ch level output to the CD mechanism controller (IC800)

5 to 7 NC

O Not used (open)

8BYTE

I External data bus line byte selection signal input “L”: 16 bit, “H”: 8 bit (fixed at “L”)

9 CNVSS

— Ground terminal

10 XIN-T

I Sub system clock input terminal Not used (open)

11 XOUT-T

O Sub system clock output terminal Not used (open)

12 S·RST I

System reset signal input “L”: reset

For several hundreds msec. after the power supply rises, “L” is input, then it changes to “H”

13 XOUT

O Main system clock output terminal (10 MHz)

14 GND

— Ground terminal

15 XIN

I Main system clock input terminal (10 MHz)

16 VCC

— Power supply terminal (+3.5V)

17

NMI I Non-maskable interrupt input terminal “L” active (fixed at “H” in this set)

18 DQSY

I

Digital In U-bit CD format subcode Q sync (SCOR) input from the CXD2662R (IC151)

“L” is input every 13.3 msec Almost all, “H” is input

19 P.DOWN

I Power down detection signal input terminal “L”: power down, normally: “H”

20 SQSY

I

Subcode Q sync (SCOR) input from the CXD2662R (IC151)

“L” is input every 13.3 msec Almost all, “H” is input

21 to 24 NC

O Not used (open)

25 XINT

I Interrupt status input from the CXD2662R (IC151)

26 NC

O Not used (open)

27 NC (CLIP)

O Serial data output terminal Not used (open)

28 NC

O Not used (open)

29 IIC CLK

I/O

Communication data reading clock signal output or transfer clock signal input with the CD

mechanism controller (IC800)

30 IIC DATA I/O

Communication data bus with the CD mechanism controller (IC800)

31

SWDT

O

Writing data output to the CXD2662R (IC151)

32 SRDT I

Reading data input from the CXD2662R (IC151)

33 SCLK O

Serial clock signal output to the CXD2662R (IC151)

34

RST1

O

Not used (open)

35 NC (CLIP)

O Serial clock signal output terminal Not used (open)

36 NC (CLIP)

O Not used (open)

37 NC (CLIP)

I Serial data input terminal Not used (open)

38 to 40

NC O Not used (open)

41

EPM I Not used (fixed at “L”)

42, 43

NC O Not used (open)

44 PROTECT I

Rec-proof claw detect input from the protect detect switch (S102-2) “H”: write protect

45 SCL O

Clock signal output to the EEPROM (IC195)

46

CE I Not used (fixed at “H”)

47 EEP-WP O

Writing protect signal output to the EEPROM (IC195)

48 XBUSY I

Busy signal input from the CXD2662R (IC151)

49 OUT-SW I

Detection input from the loading-out detect switch (S103)

“L” at a load-out position, others: “H”

50 XLATCH

O Serial data latch pulse signal output to the CXD2662R (IC151)

Loading...

Loading...