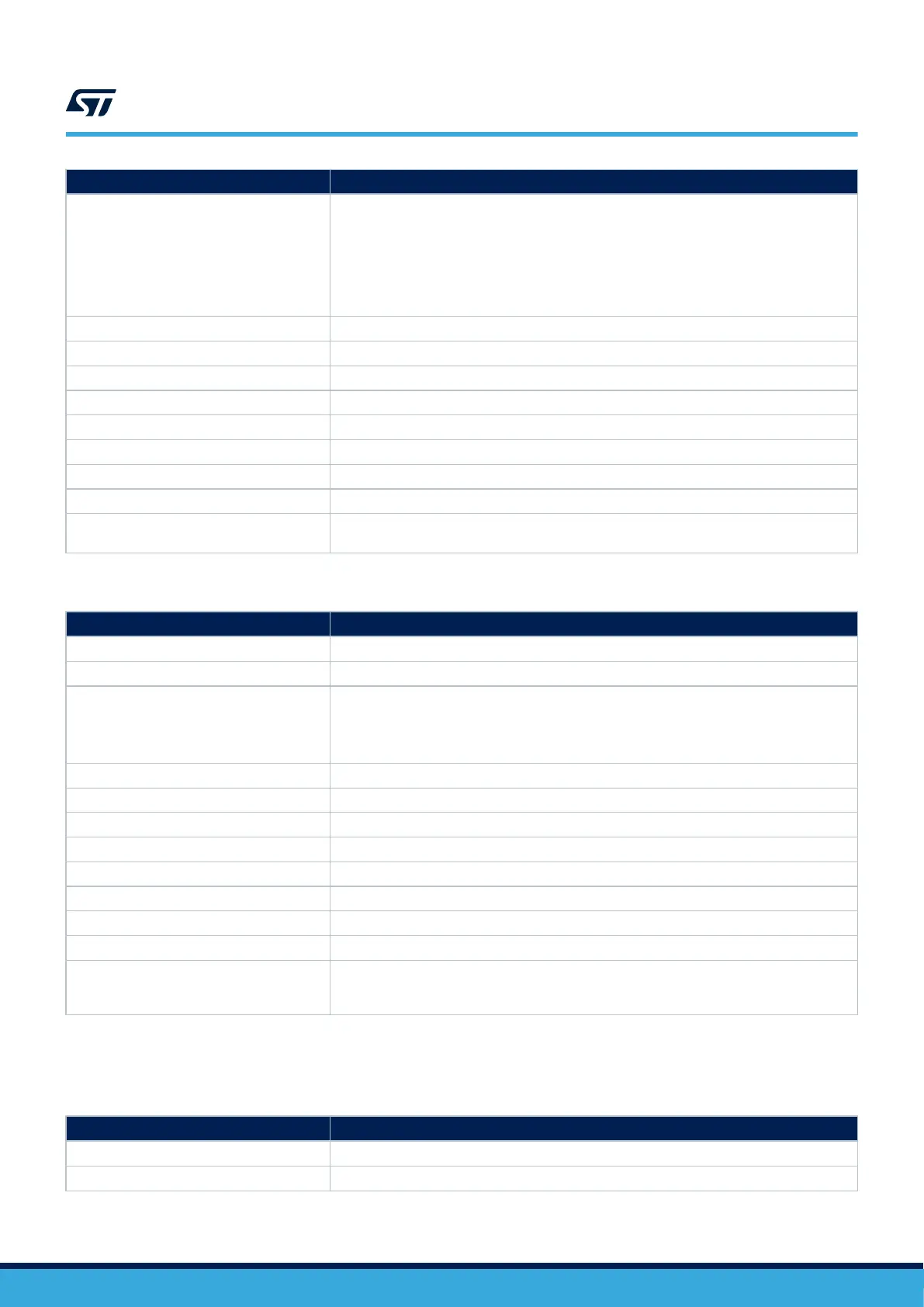

SM CODE BUS_SM_0

Detailed implementation

The intra-chip connection resources (Bus Matrix, AHB or APB bridges) needs to be

periodically tested for permanent faults detection. Note that STM32L4 and STM32L4+

Series devices have no hardware safety mechanism to protect these structures. The test

executes a connectivity test of these shared resources, including the testing of the arbitration

mechanisms between peripherals.

According to IEC 61508:2 Table A.8, A.7.4 the method is considered able to achieve high

levels of coverage.

Error reporting Depends on implementation

Fault detection time Depends on implementation

Addressed fault model Permanent

Dependency on Device configuration None

Initialization Depends on implementation

Periodicity Periodic

Test for the diagnostic Not applicable

Multiple-fault protection CPU_SM_0: Periodic core self-test software

Recommendations and known limitations

Implementation can be considered in large part as overlapping with the widely used Periodic

read-back of configuration registers required for several peripherals.

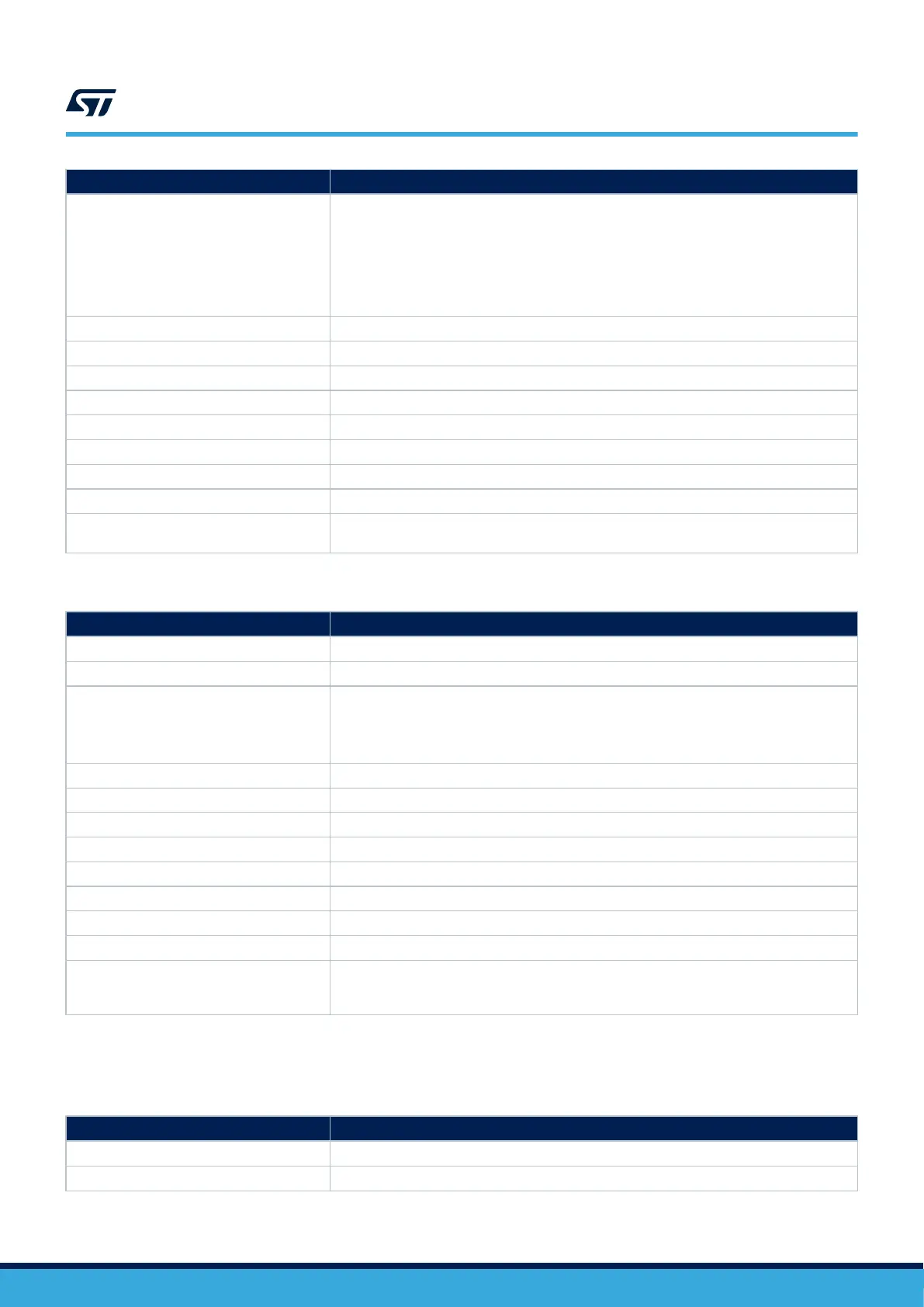

Table 15. BUS_SM_1

SM CODE BUS_SM_1

Description Information redundancy in intra-chip data exchanges

Ownership End user

Detailed implementation

This method requires to add some kind of redundancy (for example a CRC checksum at

packet level) to each data message exchanged inside Device.

Message integrity is verified using the checksum by Application software, before consuming

data.

Error reporting Depends on implementation

Fault detection time Depends on implementation

Addressed fault model Permanent/transient

Dependency on Device configuration None

Initialization Depends on implementation

Periodicity On demand

Test for the diagnostic Not applicable

Multiple-fault protection CPU_SM_0: Periodic core self-test software

Recommendations and known limitations

Implementation can be in large part overlapping with other safety mechanisms requiring

information redundancy on data messages for communication peripherals. Optimizations are

therefore possible.

3.6.3 Embedded SRAM

Table 16. RAM_SM_0

SM CODE RAM_SM_0

Description Periodic software test for static random access memory (SRAM)

Ownership End user or ST

UM2305

Hardware and software diagnostics

UM2305 - Rev 10

page 17/110

Loading...

Loading...