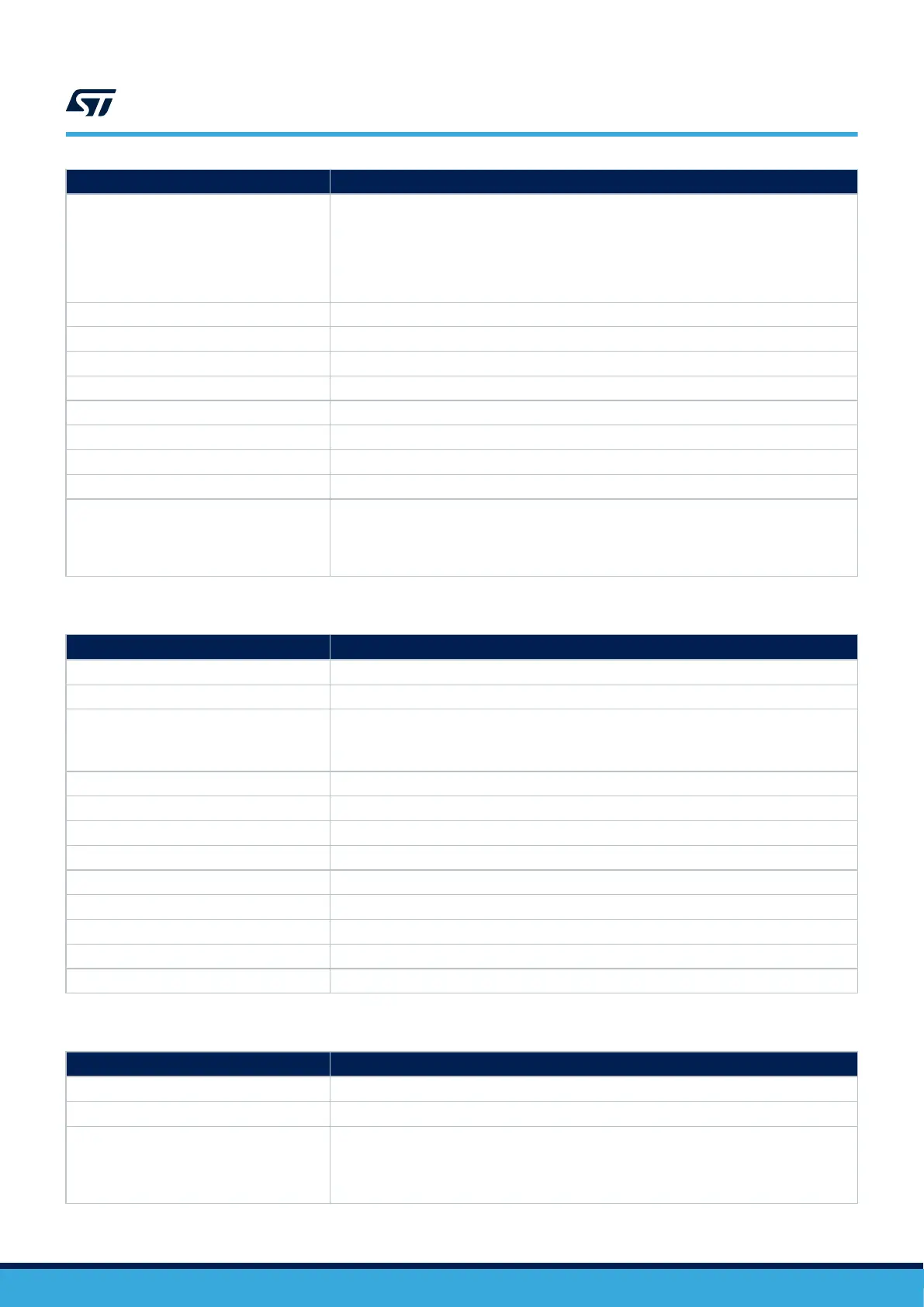

SM CODE FSMC_SM_1

Detailed implementation

If FSMC interface is used to connect an external memory where safety-relevant data are

stored, information redundancy techniques for stored data are able to address faults affecting

the FSMC interface. The possible techniques are:

• using redundant copies of safety-relevant data and performing coherence check before

consuming

• organizing data in arrays and computing the checksum field to check before use

Error reporting Depends on implementation

Fault detection time Depends on implementation

Addressed fault model Permanent/transient

Dependency on Device configuration FSMC interface is available only on selected part numbers.

Initialization Depends on implementation

Periodicity On demand

Test for the diagnostic Not applicable

Multiple-fault protection CPU_SM_0: Periodic core self-test software

Recommendations and known limitations

This mechanism must be used just if FSMC external memory is used to store safety-related

data.

This safety mechanism can overlap with information redundancy techniques implemented at

system level to address failure of physical device connected to FSMC port.

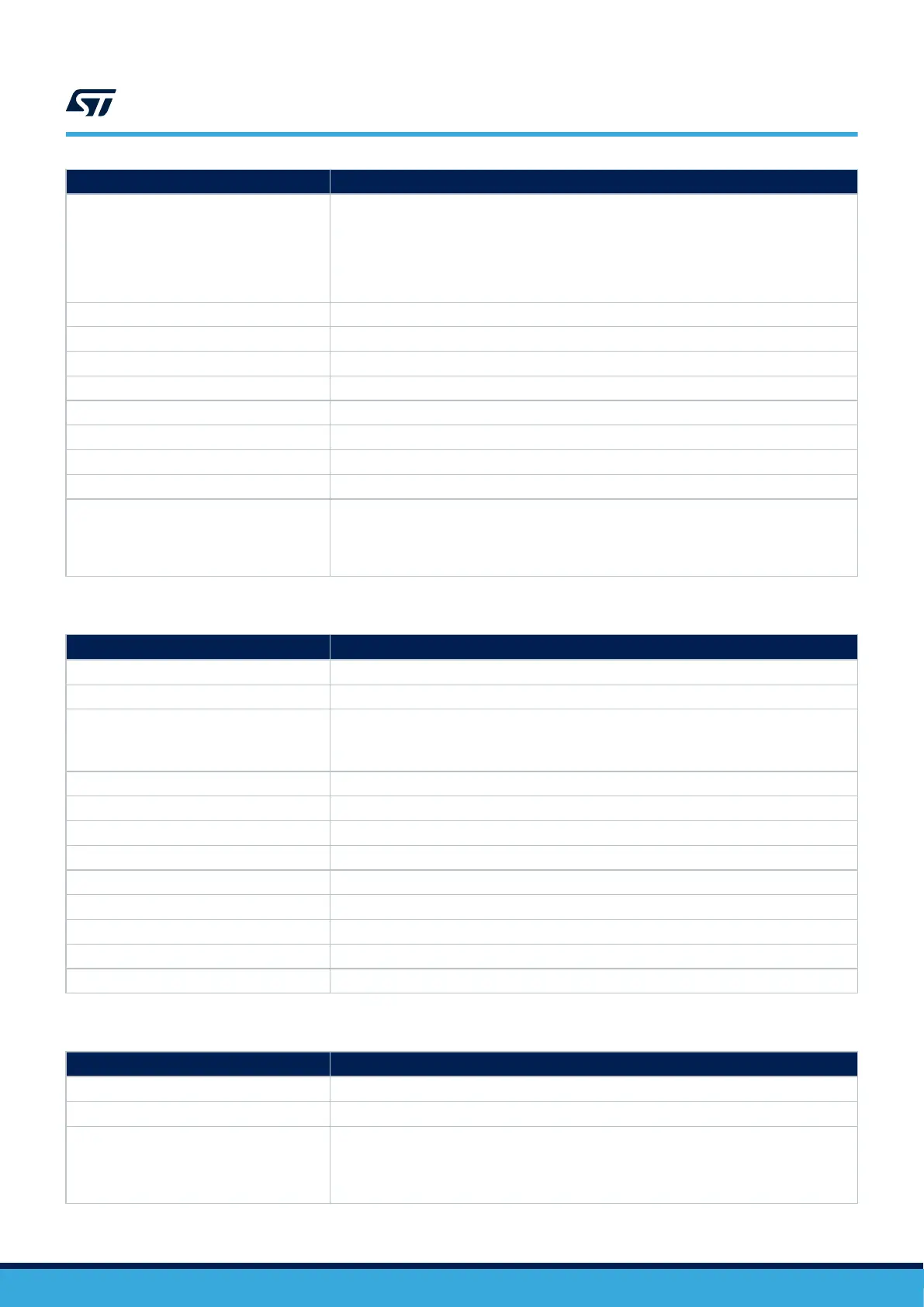

Table 67. FSMC_SM_2

SM CODE FSMC_SM_2

Description Periodic read-back of FSMC configuration registers

Ownership End user

Detailed implementation

This method must be applied to FSMC configuration registers.

Detailed information on the implementation of this method can be found in

Section 3.6.14 Extended interrupt and events controller (EXTI).

Error reporting Refer to NVIC_SM_0

Fault detection time Refer to NVIC_SM_0

Addressed fault model Refer to NVIC_SM_0

Dependency on Device configuration FSMC interface is available only on selected part numbers.

Initialization Refer to NVIC_SM_0

Periodicity Refer to NVIC_SM_0

Test for the diagnostic Refer to NVIC_SM_0

Multiple-fault protection Refer to NVIC_SM_0

Recommendations and known limitations Refer to NVIC_SM_0

Table 68. FSMC_SM_3

SM CODE FSMC_SM_3

Description ECC engine on NAND interface in FSMC module

Ownership ST

Detailed implementation

The FMC NAND Card controller includes two error correction code computation hardware

blocks, one per memory bank. They reduce the host CPU workload when processing the ECC

by software.

ECC mechanism protects data integrity on the external memory connected to NAND port.

UM2305

Hardware and software diagnostics

UM2305 - Rev 10

page 43/110

Loading...

Loading...