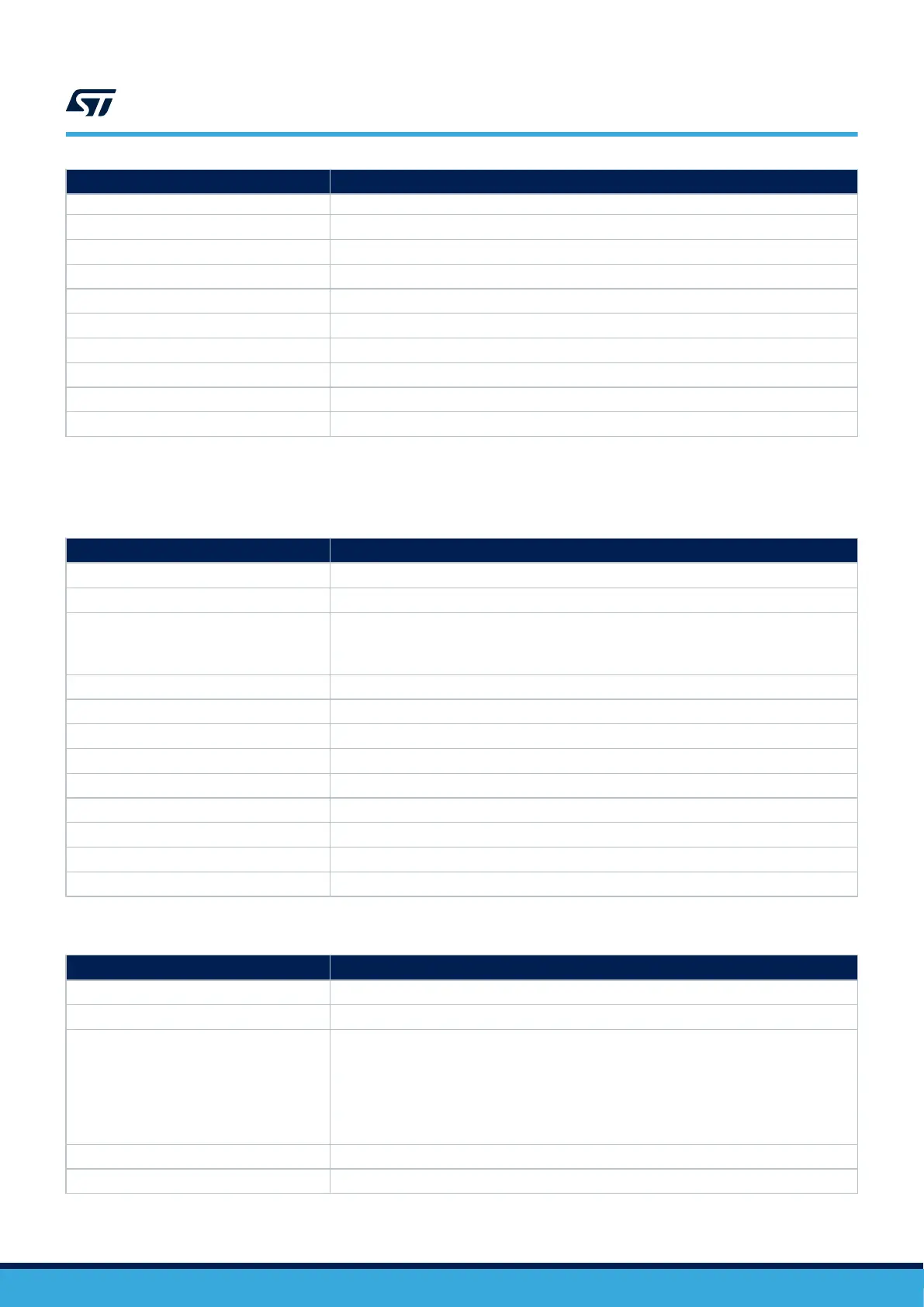

SM CODE DIAG_SM_0

• interrupt/NMI enable (if used for diagnostic error management)

Error reporting Refer to NVIC_SM_0

Fault detection time Refer to NVIC_SM_0

Addressed fault model Refer to NVIC_SM_0

Dependency on Device configuration Refer to NVIC_SM_0

Initialization Refer to NVIC_SM_0

Periodicity Refer to NVIC_SM_0

Test for the diagnostic Refer to NVIC_SM_0

Multiple-fault protection Refer to NVIC_SM_0

Recommendations and known limitations Refer to NVIC_SM_0

3.6.11 Direct memory access controller (DMA/ DMA2D/ DMAMUX))

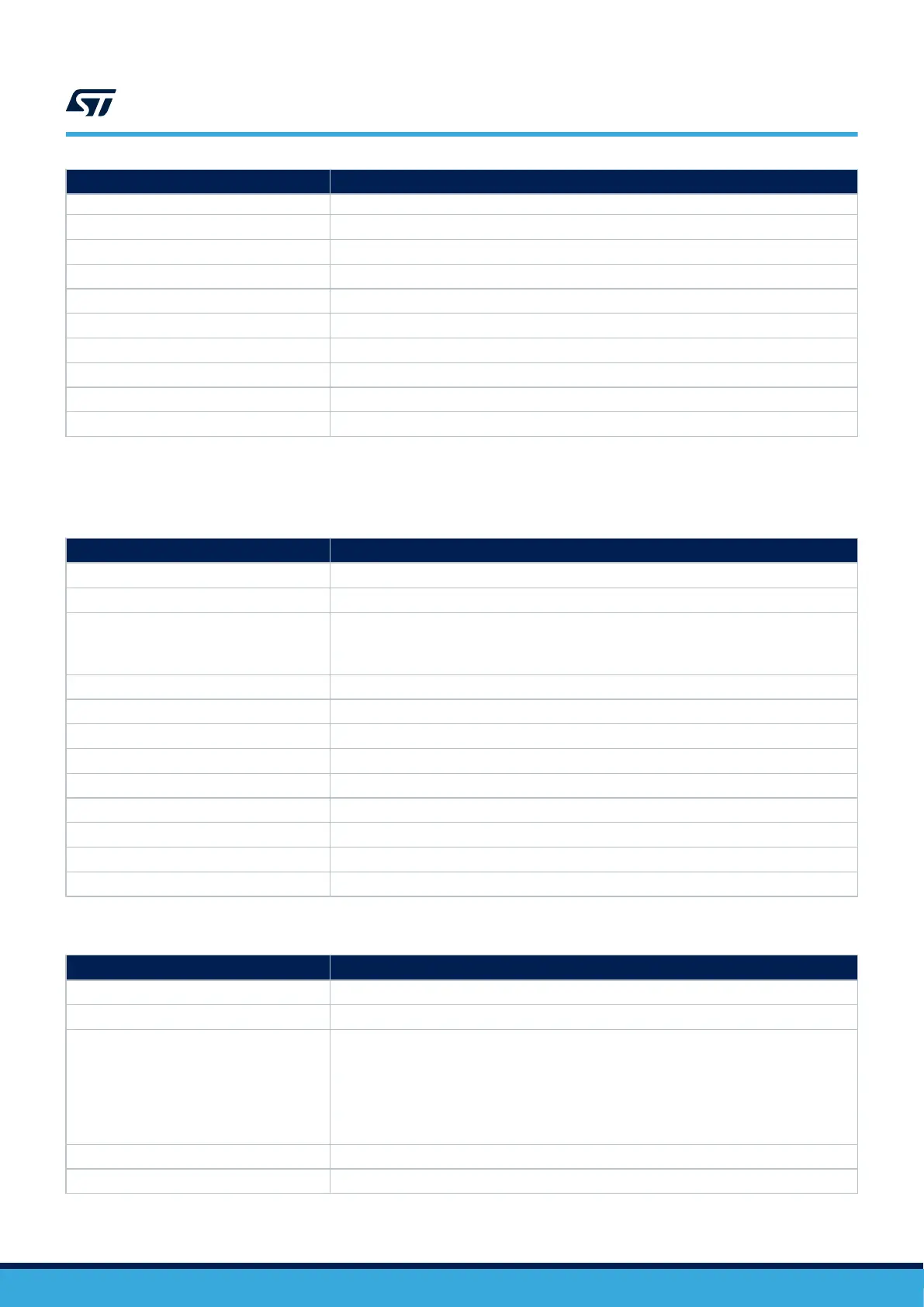

Table 52. DMA_SM_0

SM CODE DMA_SM_0

Description Periodic read-back of configuration registers

Ownership End user

Detailed implementation

This method must be applied to DMA configuration register and channel address register.

Detailed information on the implementation of this method can be found in

Section 3.6.14 Extended interrupt and events controller (EXTI).

Error reporting Refer to NVIC_SM_0

Fault detection time Refer to NVIC_SM_0

Addressed fault model Refer to NVIC_SM_0

Dependency on Device configuration Refer to NVIC_SM_0

Initialization Refer to NVIC_SM_0

Periodicity Refer to NVIC_SM_0

Test for the diagnostic Refer to NVIC_SM_0

Multiple-fault protection Refer to NVIC_SM_0

Recommendations and known limitations Refer to NVIC_SM_0

Table 53. DMA_SM_1

SM CODE DMA_SM_1

Description Information redundancy on data packet transferred via DMA

Ownership End user

Detailed implementation

This method is implemented by adding, to data packets transferred by DMA, a redundancy

check (such as CRC check or similar one) with encoding capability. Full data packet

redundancy would be an overkill.

The checksum encoding capability must be robust enough to guarantee at least 90%

probability of detection for a single bit flip in the data packet.

Consistency of data packet must be checked by Application software before consuming data.

Error reporting Depends on implementation

Fault detection time Depends on implementation

UM2305

Hardware and software diagnostics

UM2305 - Rev 10

page 35/110

Loading...

Loading...