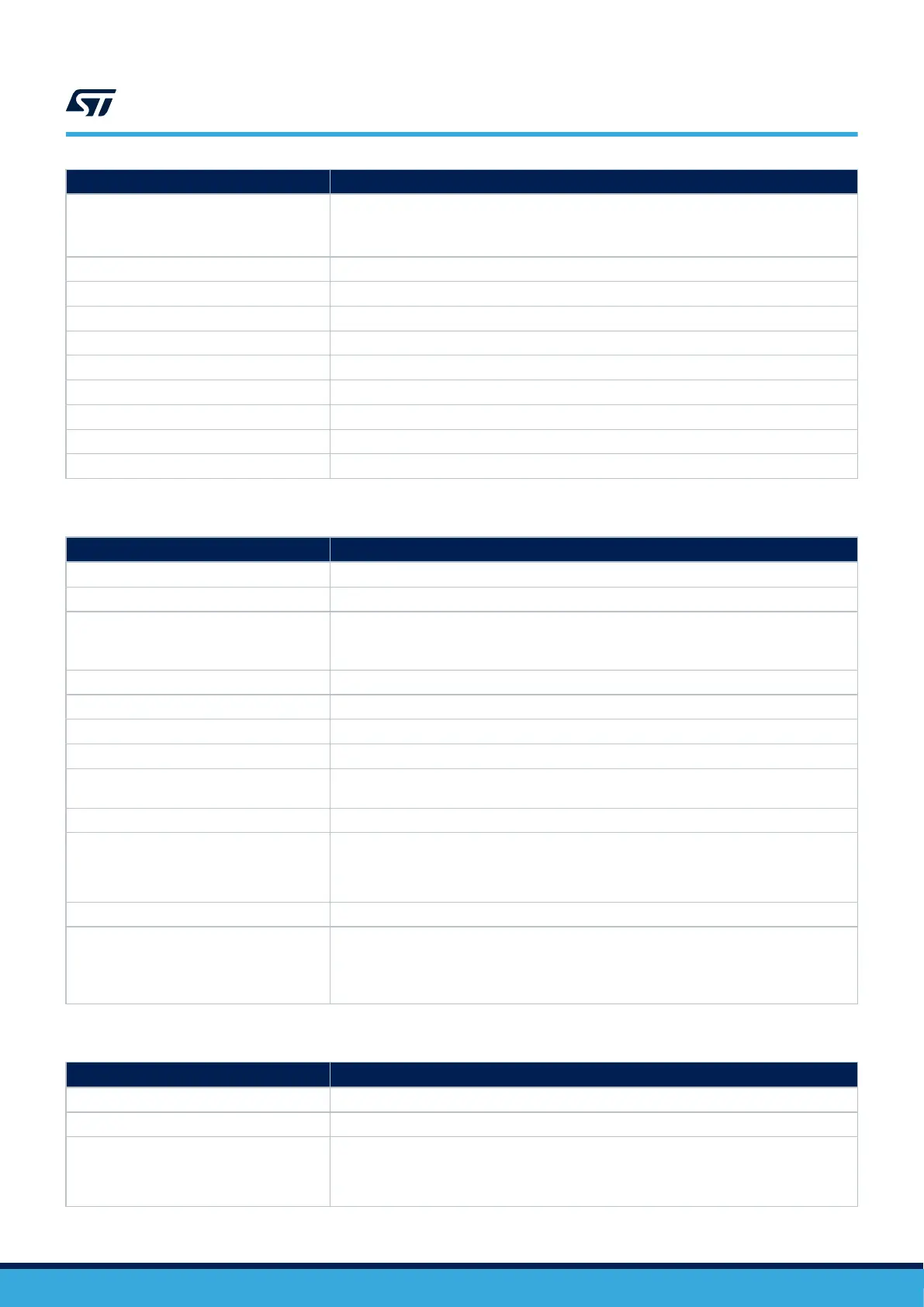

SM CODE VSUP_SM_0

Detailed implementation

This method must be applied to configuration registers.

Detailed information on the implementation of this method can be found in

Section 3.6.14 Extended interrupt and events controller (EXTI).

Error reporting Refer to NVIC_SM_0

Fault detection time Refer to NVIC_SM_0

Addressed fault model Refer to NVIC_SM_0

Dependency on Device configuration Refer to NVIC_SM_0

Initialization Refer to NVIC_SM_0

Periodicity Refer to NVIC_SM_0

Test for the diagnostic Refer to NVIC_SM_0

Multiple-fault protection Refer to NVIC_SM_0

Recommendations and known limitations Refer to NVIC_SM_0

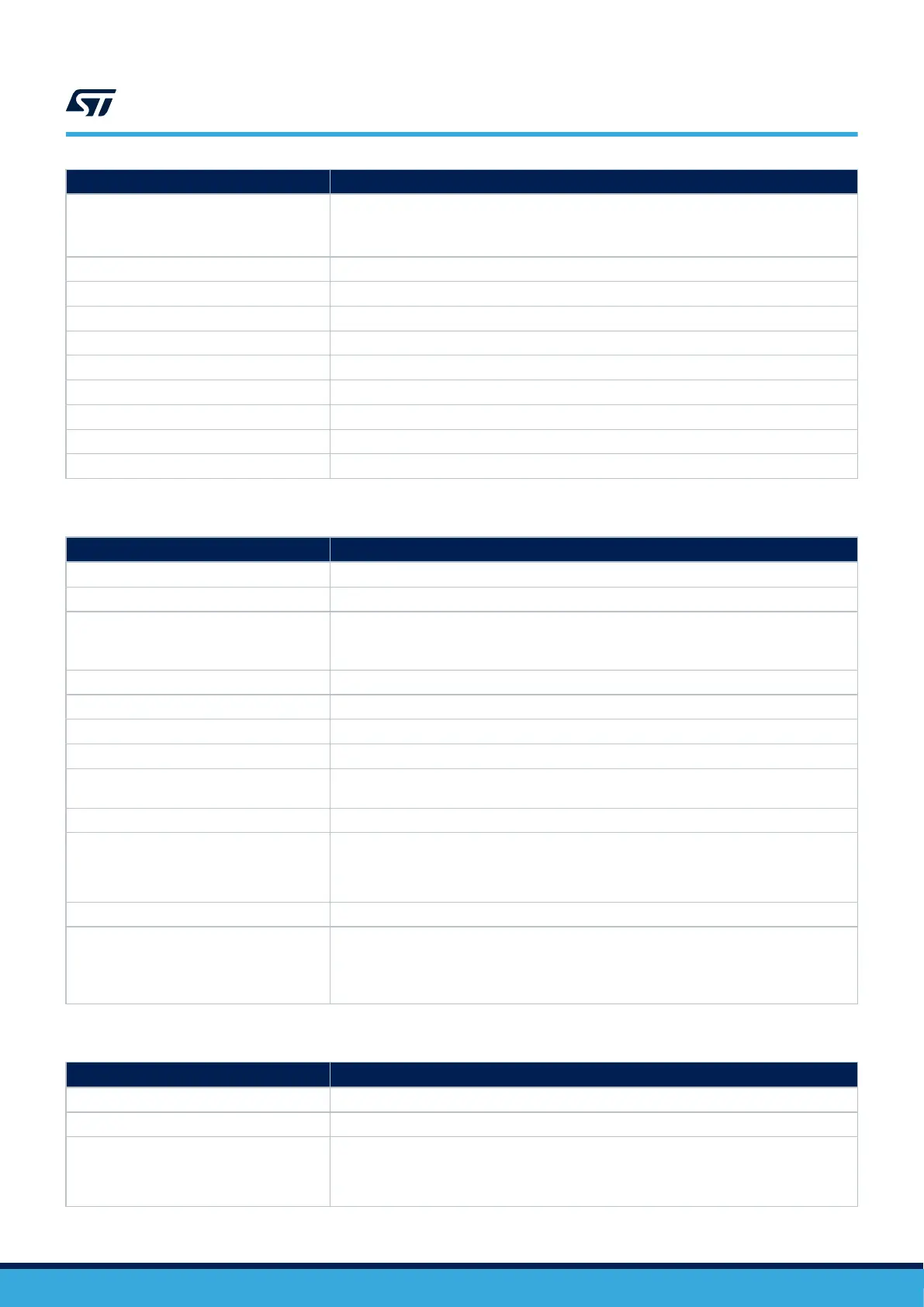

Table 35. VSUP_SM_1

SM CODE VSUP_SM_1

Description Supply voltage internal monitoring (PVD)

Ownership ST

Detailed implementation

The device features an embedded programmable voltage detector (PVD) that monitors the

V

DD

power supply and compares it to the V

PVD

threshold. An interrupt can be generated when

V

DD

drops below the V

PVD

threshold or when V

DD

is higher than the V

PVD

threshold.

Error reporting Interrupt event generation

Fault detection time Depends on threshold programming. Refer to functional documentation.

Addressed fault model Permanent/transient

Dependency on Device configuration None

Initialization

Protection enable by the PVDE bit and the threshold setting in the Power control register

(PWR_CR)

Periodicity Continuous

Test for the diagnostic

Direct test procedure for PVD efficiency is not available. PVD run-time hardware failures

leading to disabling such protection fall into multiple-fault scenario, from IEC61508

perspective. Related failures are adequately mitigated by the combination of safety

mechanisms reported in this table, field Multiple-fault protection.

Multiple-fault protection DIAG_SM_0: Periodic read-back of hardware diagnostics configuration registers

Recommendations and known limitations

Internal monitoring PVD has limited capability to address failures affecting STM32L4 and

STM32L4+ Series internal voltage regulator. Refer to [1] for details.

Internal monitoring PVD has limited capability to address failures affecting the internal voltage

regulator. Refer to Device FMEA for details.

Table 36. VSUP_SM_2

SM CODE VSUP_SM_2

Description Independent watchdog

Ownership ST

Detailed implementation

Failures in the power supplies for digital logic (core or peripherals) may lead to alteration of

Application software timing, which can be detected by IWDG as safety mechanism introduced

to monitor Application software control flow. Refer to CPU_SM_1 and CPU_SM_6 for further

information.

UM2305

Hardware and software diagnostics

UM2305 - Rev 10

page 27/110

Loading...

Loading...