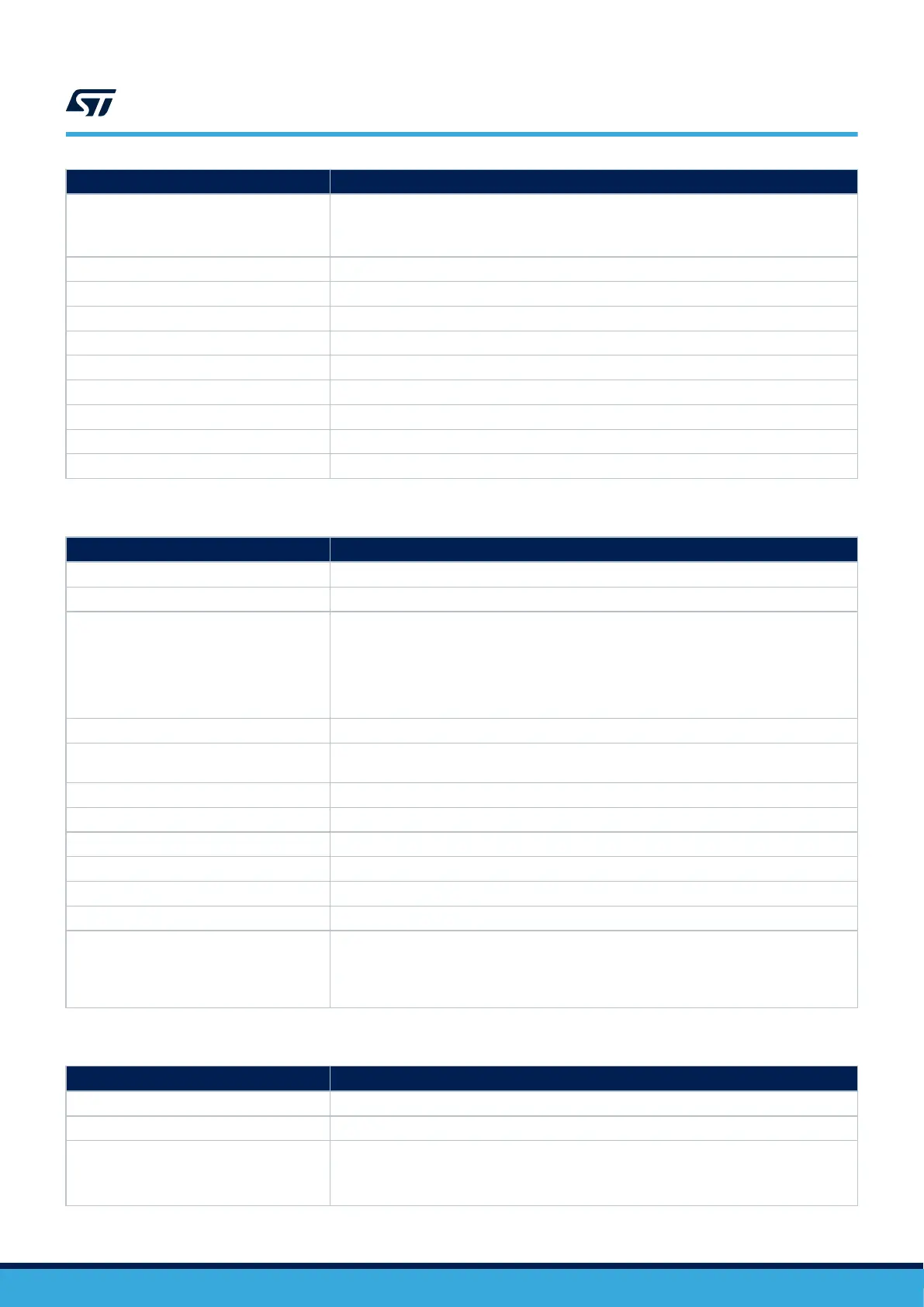

SM CODE UART_SM_0

Detailed implementation

This method must be applied to USART1/2/3/4/5/6/7/8 and LPUART configuration registers.

Detailed information on the implementation of this method can be found in

Section 3.6.14 Extended interrupt and events controller (EXTI).

Error reporting Refer to NVIC_SM_0

Fault detection time Refer to NVIC_SM_0

Addressed fault model Refer to NVIC_SM_0

Dependency on Device configuration Refer to NVIC_SM_0

Initialization Refer to NVIC_SM_0

Periodicity Refer to NVIC_SM_0

Test for the diagnostic Refer to NVIC_SM_0

Multiple-fault protection Refer to NVIC_SM_0

Recommendations and known limitations Refer to NVIC_SM_0

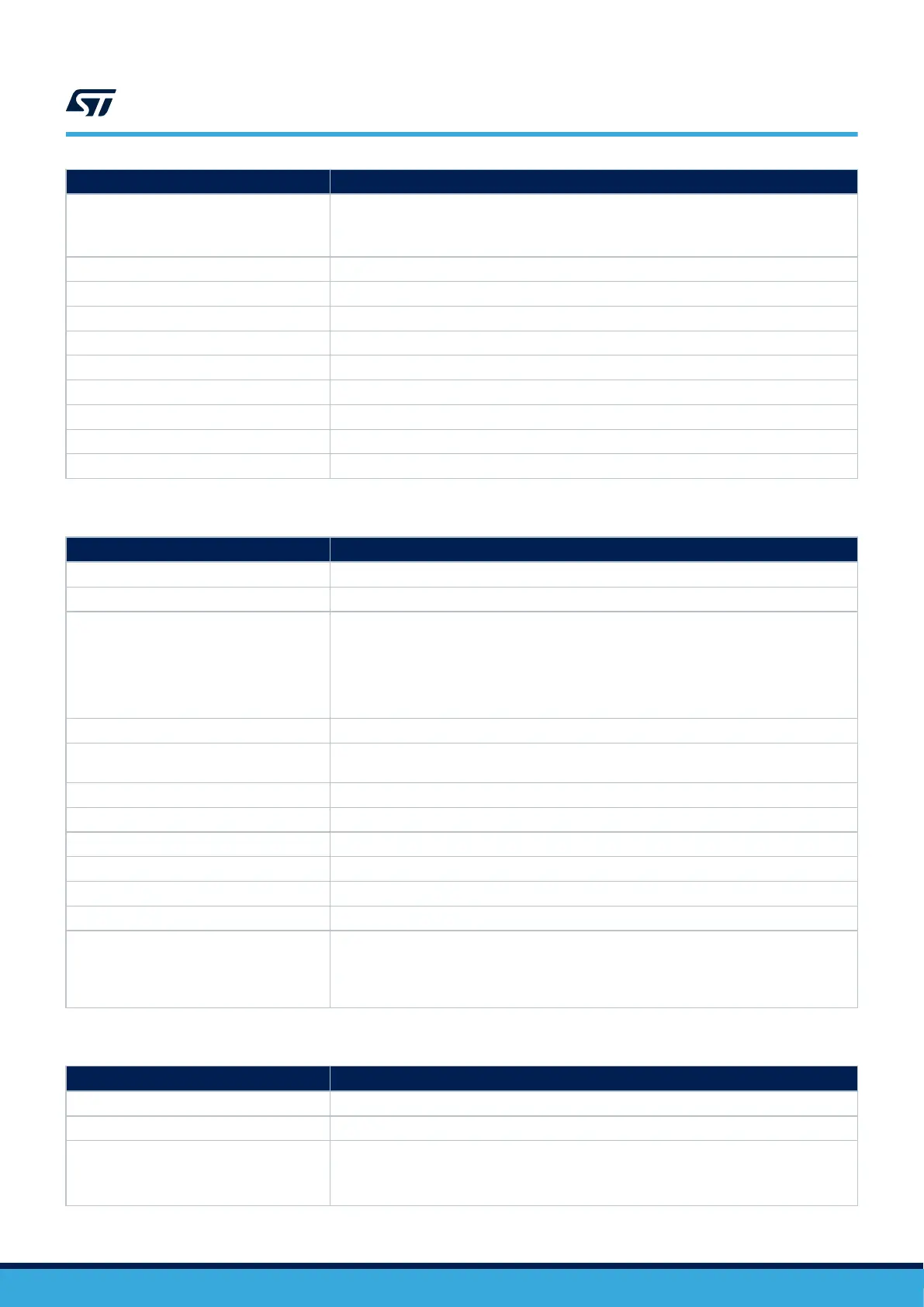

Table 124. UART_SM_1

SM CODE UART_SM_1

Description Protocol error signals

Ownership ST

Detailed implementation

USART1/2/3/4/5/6/7/8 and LPUART communication module embeds protocol error checks

(like additional parity bit check, overrun, frame error) conceived to detect network-related

abnormal conditions. These mechanisms are able anyway to detect a marginal percentage of

hardware random failures affecting the module itself.

Error signals connected to these checkers are normally handled in a standard communication

software, so the overhead is reduced.

Error reporting Error flag raise and optional interrupt event generation

Fault detection time

Depends on peripheral configuration (for example baud rate). Refer to functional

documentation.

Addressed fault model Permanent/transient

Dependency on Device configuration None

Initialization Depends on implementation

Periodicity Continuous

Test for the diagnostic Not applicable

Multiple-fault protection UART_SM_2: Information redundancy techniques on messages

Recommendations and known limitations

USART1/2/3/4/5/6/7/8 and LPUART communication module allows several different

configurations. The actual composition of communication error checks depends on the

selected configuration.

Enabling related interrupt generation on the detection of errors is highly recommended.

Table 125. UART_SM_2

SM CODE UART_SM_2

Description Information redundancy techniques on messages

Ownership End user

Detailed implementation

This method is implemented by adding to data packets transferred by USART1/2/3/4/5/6/7/8

and LPUART a redundancy check (such as a CRC check, or similar one) with encoding

capability. The checksum encoding capability must be robust enough to guarantee at least

90% probability of detection for a single bit flip in the data packet.

UM2305

Hardware and software diagnostics

UM2305 - Rev 10

page 70/110

Loading...

Loading...