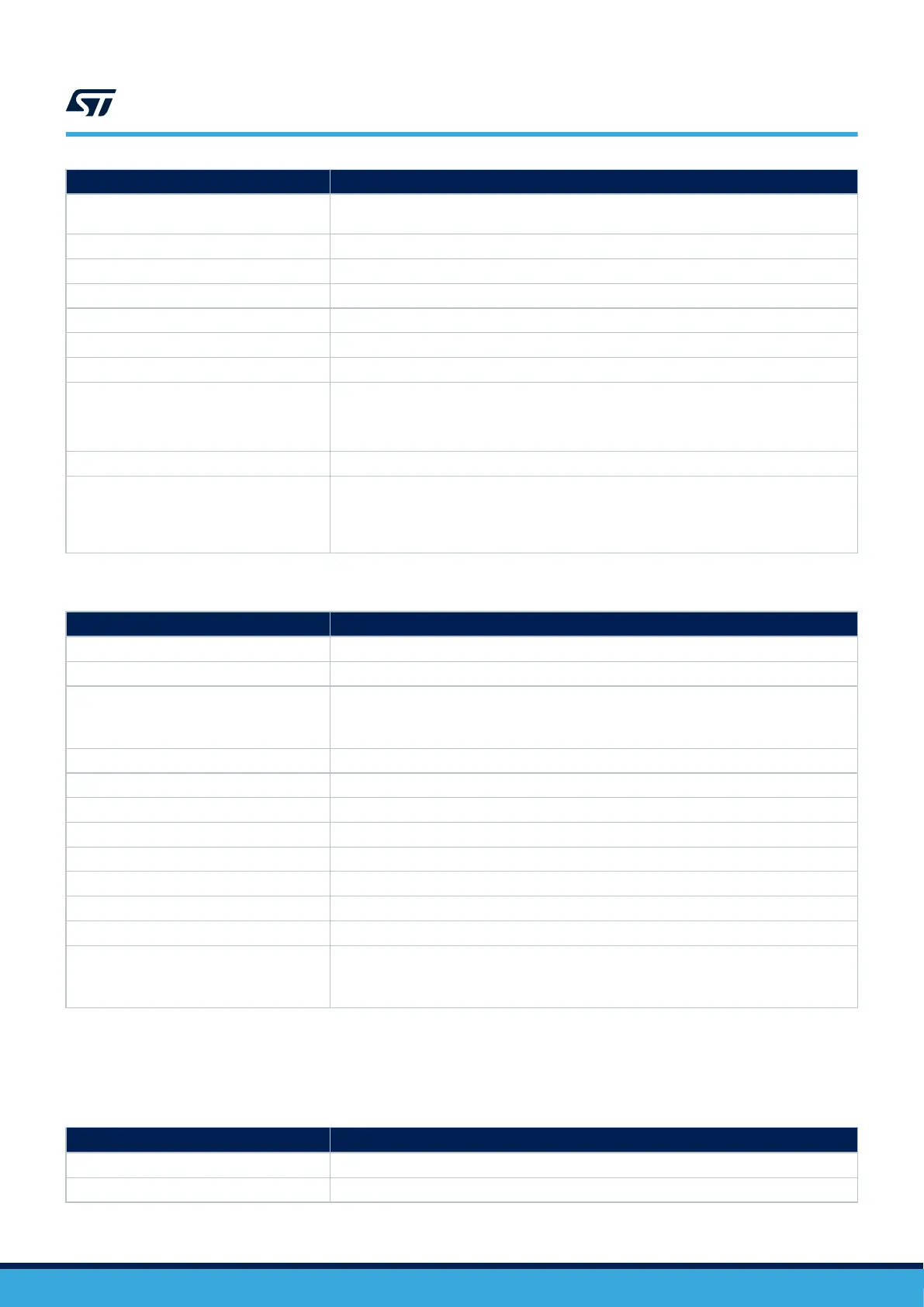

SM CODE IIC_SM_3

Detailed implementation

I2C communication module allows to activate for specific mode of operation (SMBus) the

automatic insertion (and check) of CRC checksums to packet data.

Error reporting Error flag raise and optional Interrupt Event generation

Fault detection time Depends on implementation

Addressed fault model Permanent/transient

Dependency on Device configuration None

Initialization Depends on implementation

Periodicity Continuous

Test for the diagnostic

Direct test procedure for CRC efficiency is not available. CRC run-time hardware failures

leading to disabling such protection fall into multiple-fault scenario, from IEC61508

perspective. Related failures are adequately mitigated by the combination of safety

mechanisms reported in this table, field Multiple-fault protection.

Multiple-fault protection IIC_SM_2: Information redundancy techniques on messages

Recommendations and known limitations

This method can be part of the implementation for IIC_SM_2 or IIC_SM_4. In that case,

because of the warning issued in the Test for the diagnostic field, this mechanism can not be

the only one to guarantee message integrity.

Enabling related interrupt generation on the detection of errors is highly recommended.

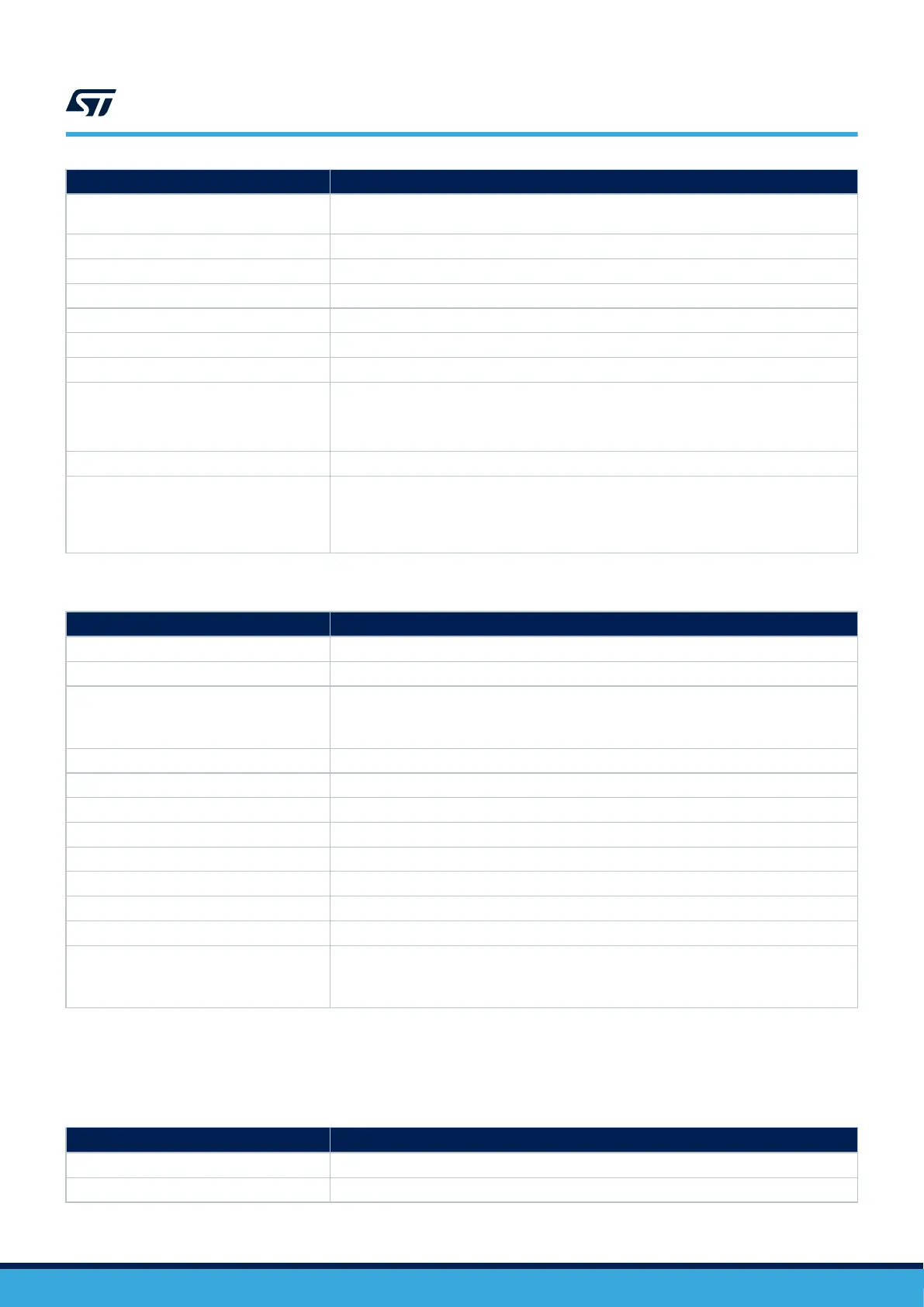

Table 122. IIC_SM_4

SM CODE IIC_SM_4

Description Information redundancy techniques on messages, including end-to-end protection

Ownership End user

Detailed implementation

This method aims to protect the communication between a I2C peripheral and his external

counterpart.

Refer to UART_SM_3 description for detailed information.

Error reporting Refer to UART_SM_3

Fault detection time Refer to UART_SM_3

Addressed fault model Refer to UART_SM_3

Dependency on Device configuration Refer to UART_SM_3

Initialization Refer to UART_SM_3

Periodicity Refer to UART_SM_3

Test for the diagnostic Refer to UART_SM_3

Multiple-fault protection Refer to UART_SM_3

Recommendations and known limitations

It is assumed that the remote I2C counterpart has an equivalent capability of performing the

checks described.

Refer to UART_SM_3 for further notice.

3.6.35 Universal synchronous/asynchronous receiver/transmitter and low power universal

asychronous receiver/transmitter (USART1/2/3/4/5/6/7/8 and LPUART)

Table 123. UART_SM_0

SM CODE UART_SM_0

Description Periodic read-back of configuration registers

Ownership End user

UM2305

Hardware and software diagnostics

UM2305 - Rev 10

page 69/110

Loading...

Loading...