SM CODE SWPMI_SM_0

Addressed fault model Refer to NVIC_SM_0

Dependency on Device configuration Refer to NVIC_SM_0

Initialization Refer to NVIC_SM_0

Periodicity Refer to NVIC_SM_0

Test for the diagnostic Refer to NVIC_SM_0

Multiple-fault protection Refer to NVIC_SM_0

Recommendations and known limitations Refer to NVIC_SM_0

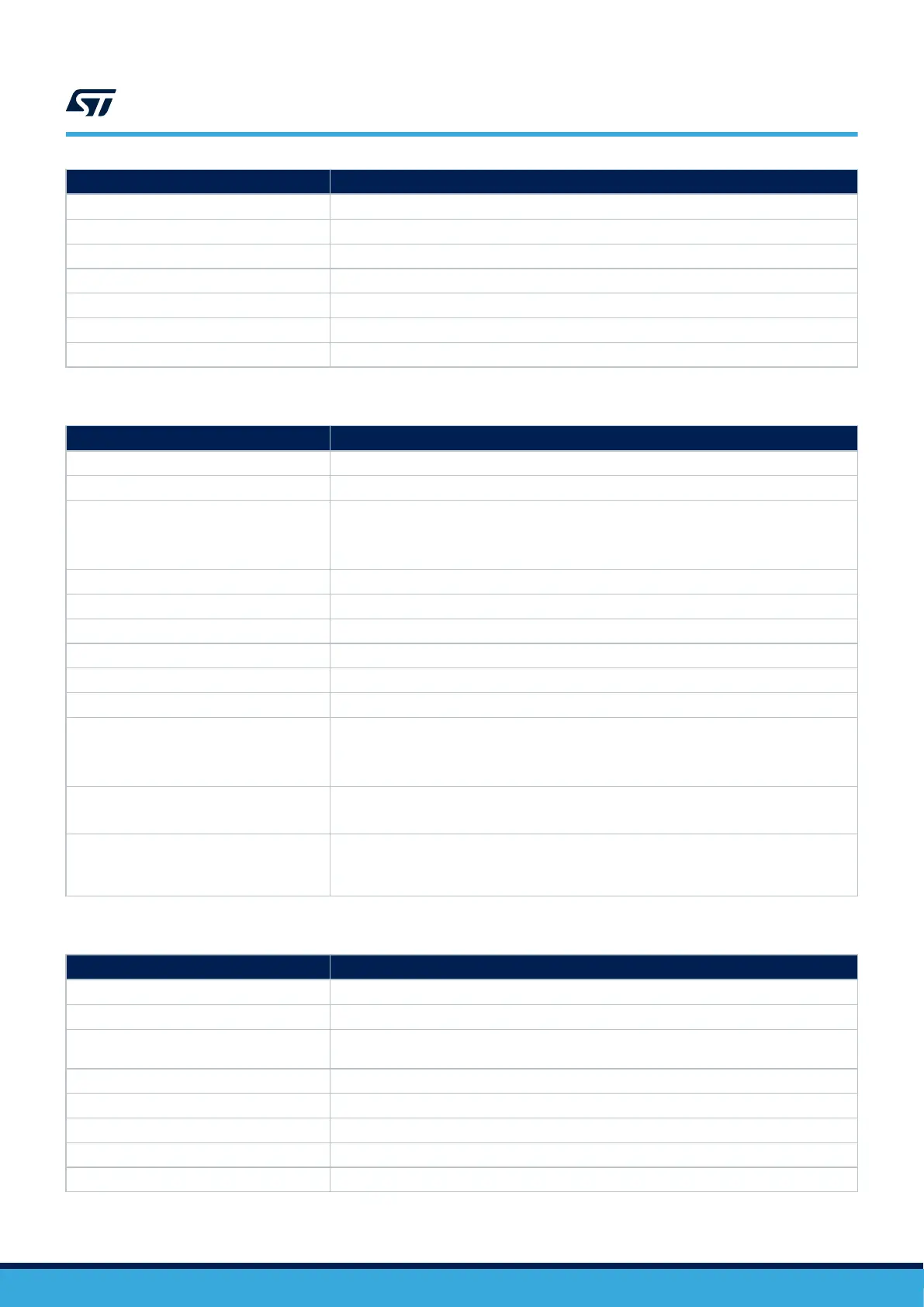

Table 136. SWPMI_SM_1

SM CODE SWPMI_SM_1

Description Protocol error signals and information redundancy including hardware CRC

Ownership ST

Detailed implementation

SWPMI communication is based on a frame handling concept, composed by a combination

of hardware synchronization signals, frame structure composition, hardware-computed CRC

filed. This mechanism, mainly implemented to manage on-field communication disturbance, is

able to achieve a relevant diagnostic coverage on several SWMPI module failure modes.

Error reporting Error conditions are reported by flag bits in related registers.

Fault detection time Depends on implementation

Addressed fault model Permanent/transient

Dependency on Device configuration None

Initialization Depends on implementation

Periodicity Continuous

Test for the diagnostic

Direct test procedure for CRC efficiency is not available. CRC run-time hardware failures

leading to disabling such protection fall into multiple-fault scenario, from IEC61508

perspective. Related failures are adequately mitigated by the combination of safety

mechanisms reported in this table, field Multiple-fault protection.

Multiple-fault protection

SWPMI_SM_0: Periodic read-back of configuration registers

SWPMI_SM_2: SWMPI loopback test

Recommendations and known limitations

This method is unable to address all IEC 61508 failure modes related to time handshake

between parties (e.g. resequencing, repetition), leading to the introduction of SWPMI_SM_3.

Enabling related interrupt generation on the detection of errors is highly recommended.

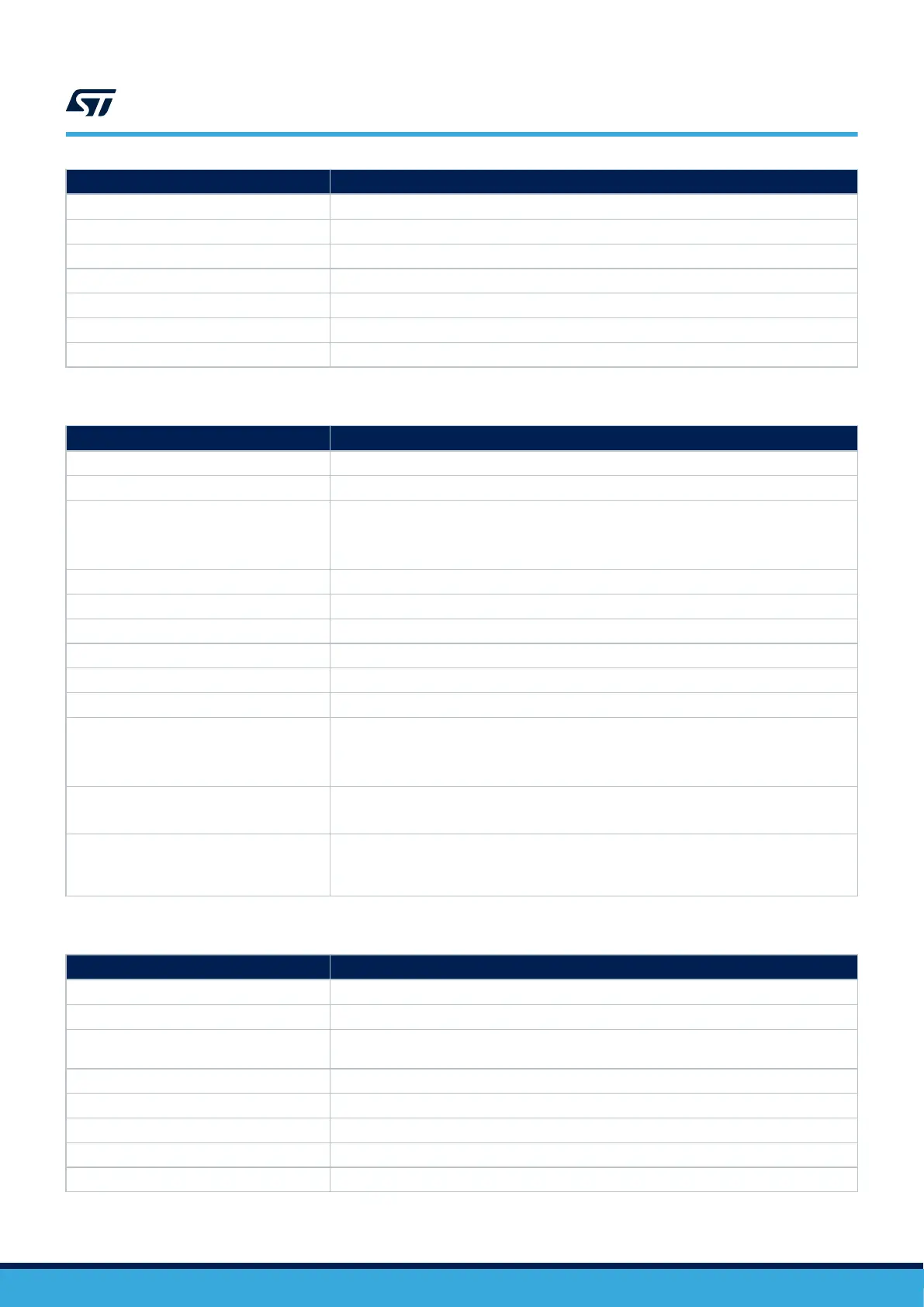

Table 137. SWPMI_SM_2

SM CODE SWPMI_SM_2

Description SWMPI loopback test

Ownership End user

Detailed implementation

By using the SWPMI module loopback function, it is possible to emulate the sending of SWPI

frames and cross-checking the expected result in reception.

Error reporting Error conditions are reported by flag bits in related registers

Fault detection time Depends on implementation

Addressed fault model Permanent

Dependency on Device configuration None

Initialization Loopback mode must be enabled.

UM2305

Hardware and software diagnostics

UM2305 - Rev 10

page 76/110

Loading...

Loading...